## **EFFICIENT FILTER CONNECTION**

Mohamed AlAlami Senior Field Application Engineer

WURTH ELEKTRONIK MORE THAN YOU EXPECT

#### <u>Agenda</u>

- Component parasitics

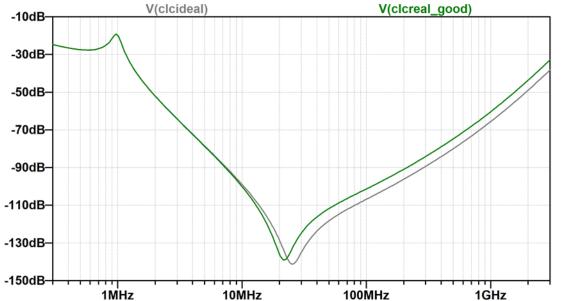

- Comparison ideal vs. real

- PCB parasitics

- Effects of multiple Vias in relation to their arrangement

- Simulation of real filters with Bias effects and Vias

#### **Overview**

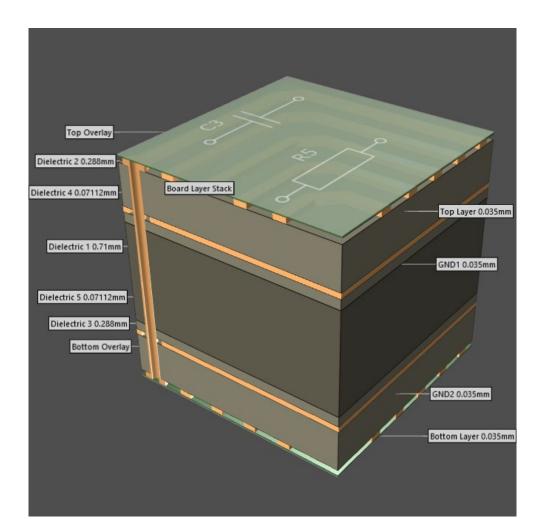

PCB and layer stack

# PARASITICS

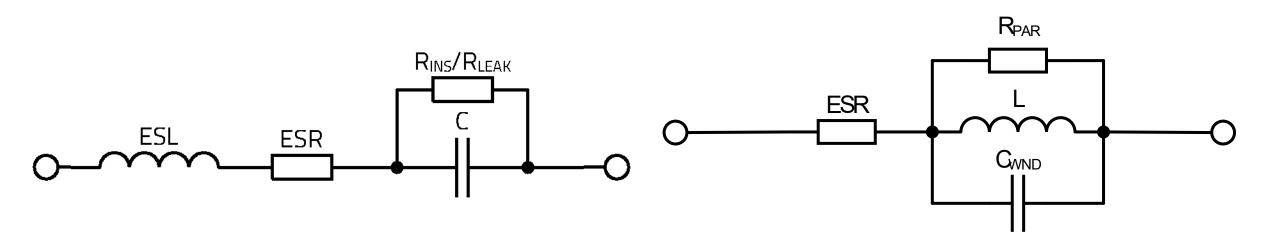

#### **Component parasitics**

Capacitor vs. inductor (ferrite)

- capacitor

- ESL

- ESR

- R<sub>LEAK</sub>

- C

- inductor (ferrite)

- ESR

- R<sub>PAR</sub>

- C<sub>WND</sub>

- L

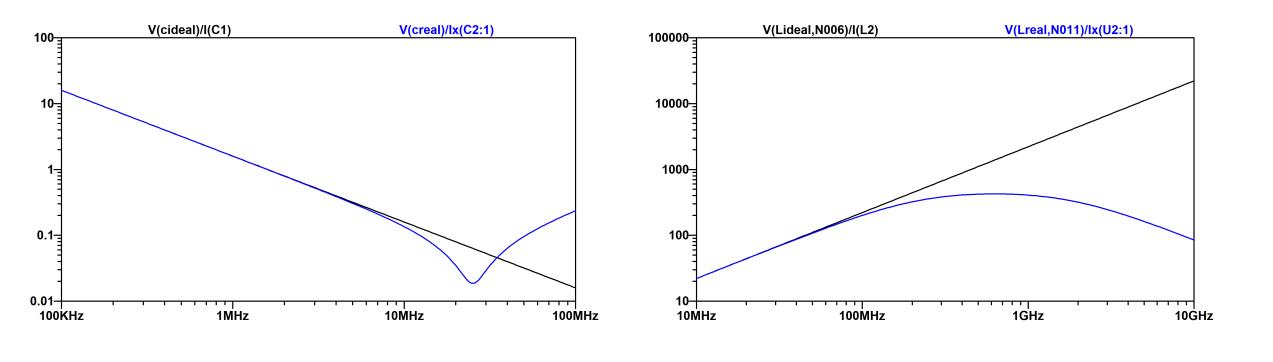

#### **Comparison Ideal vs. real**

Capacitor vs. inductor (ferrite)

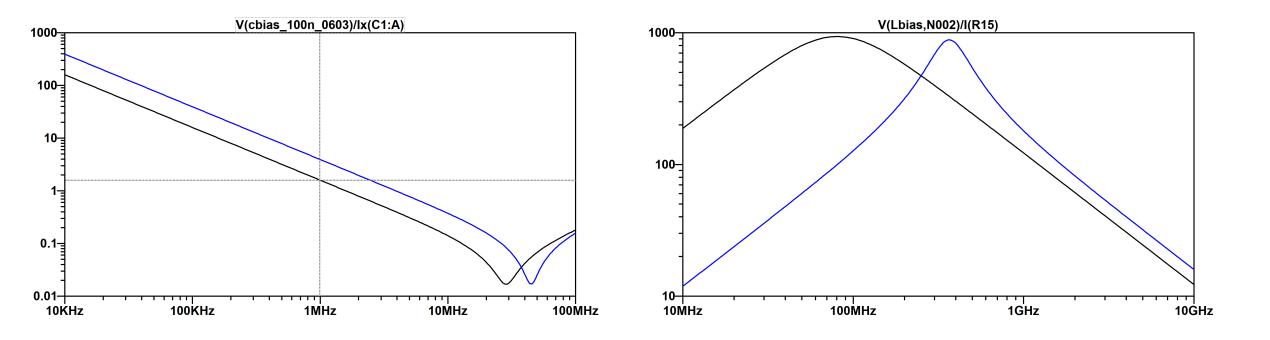

ideal vs. real capacitor

ideal vs. real inductor (ferrite)

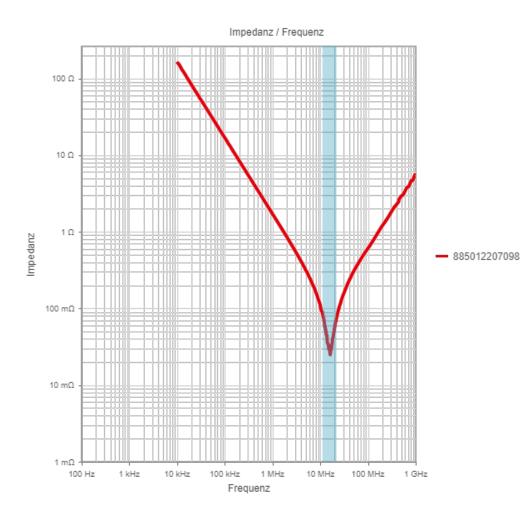

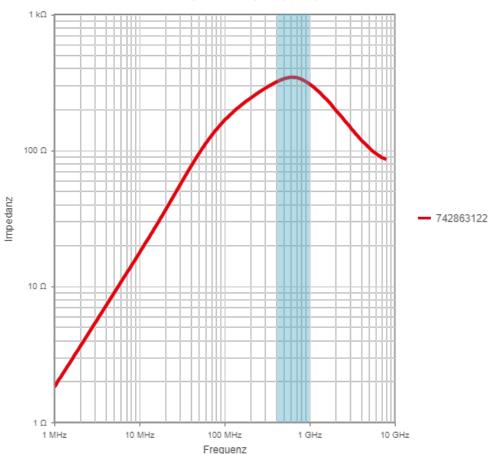

#### **Component parasitics in detail**

#### Capacitor vs. inductor (ferrite)

Impedanz / Frequenz (0,00 A)

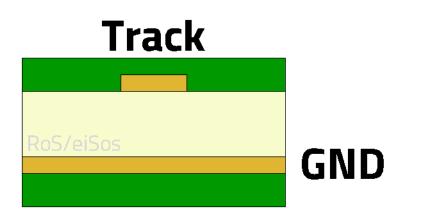

### **PCB parasitics**

Tracks

| w [mm] | h [mm] | ind [nH/mm] | cap [pF/mm] | E <sub>r</sub> |

|--------|--------|-------------|-------------|----------------|

| 0.4    | 1.6    | ~0.7        | ~0.05       | 4.6            |

| 0.2    | 1.6    | ~0.8        | ~0.04       | 4.6            |

| 0.4    | 0.288  | ~0.35       | ~0.1        | 4.6            |

| 0.2    | 0.288  | ~0.45       | ~0.07       | 4.6            |

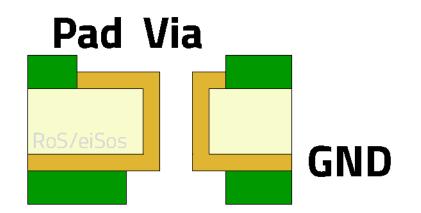

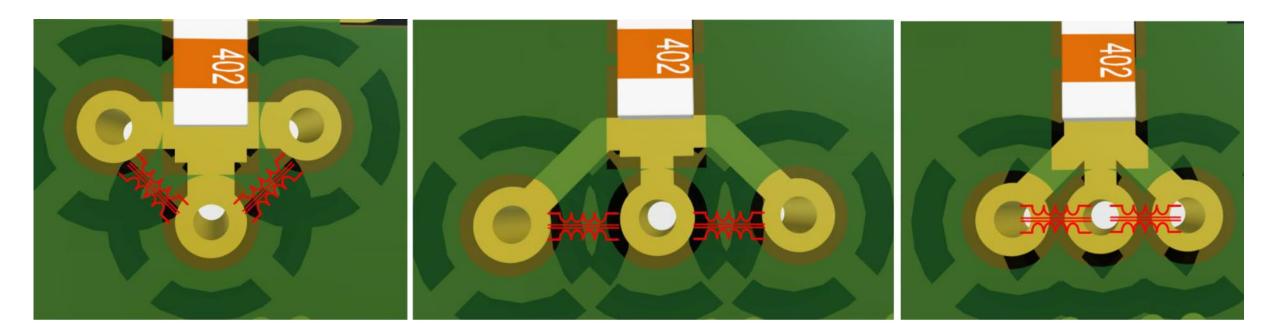

### **PCB** parasitics

Vias

- Via {d=0.3mm; h=1.6mm; 25µ plating}

- inductance: 1.3nH

- Via {d=0.3mm; h=0.288mm; 25µ plating}

- inductance: 0.14nH

- Via {d=0.3mm; h=1.6mm; 25µ plating}

- inductance: 1.3nH

- capacitance: 0.6pF {Pad=0.6mm; opening=1.0mm;  $\varepsilon_r$ =4.6}

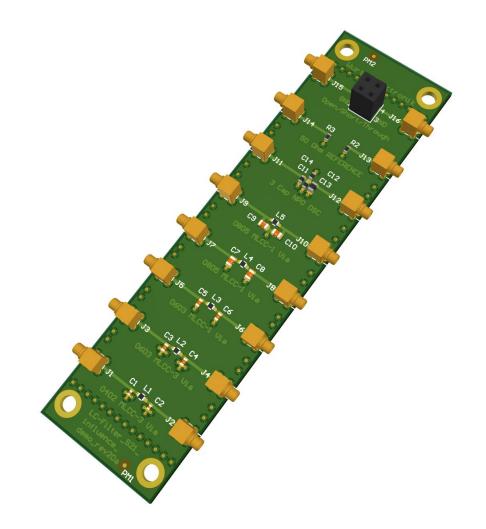

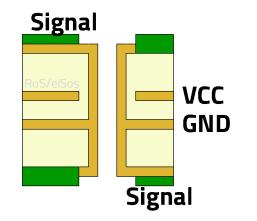

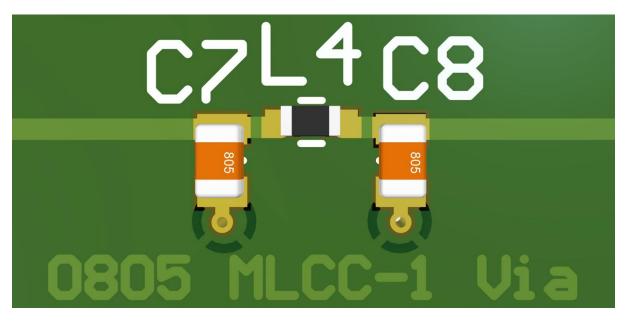

Good board realization

Real models without layout and placement influence

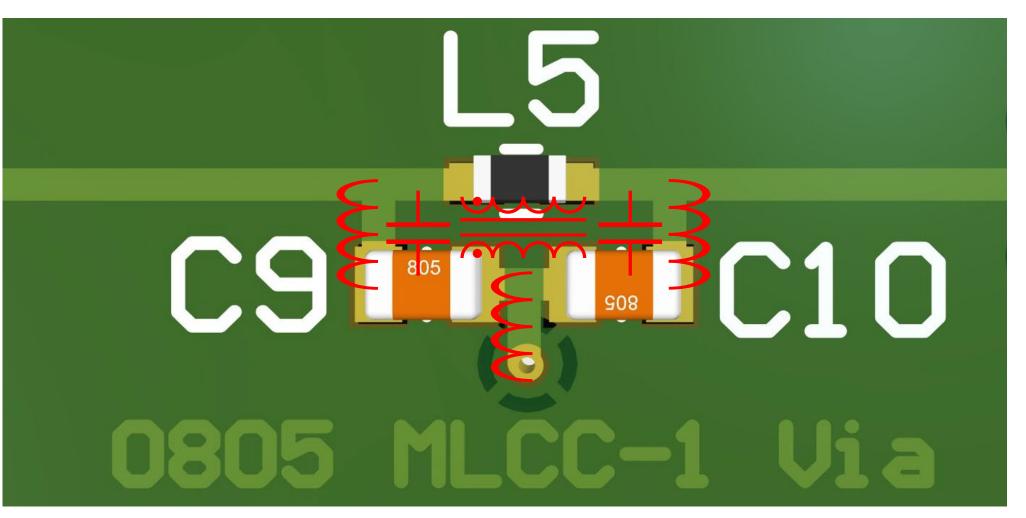

Bad board realiziation – parasitics and couplings

Simulation with parasites but without coupling

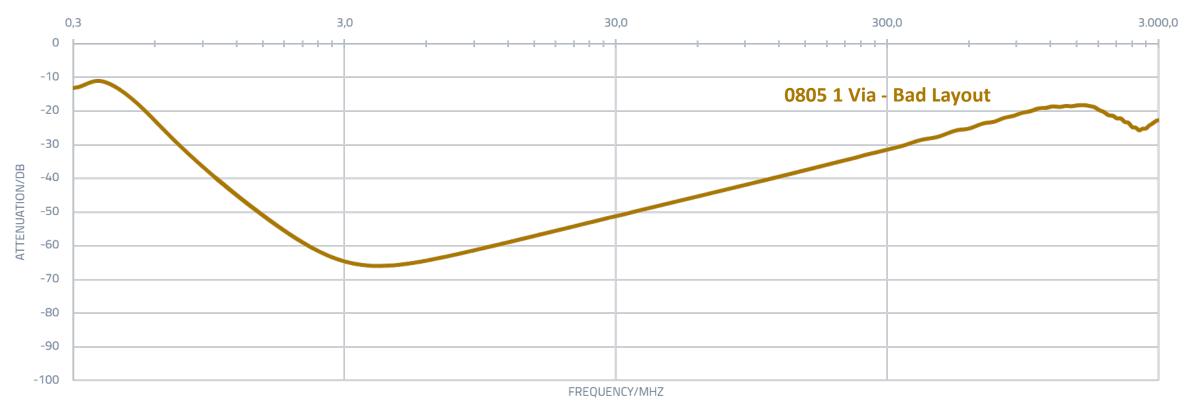

Measuring of insertion loss in parallel PLACEMENT design with coupling effects

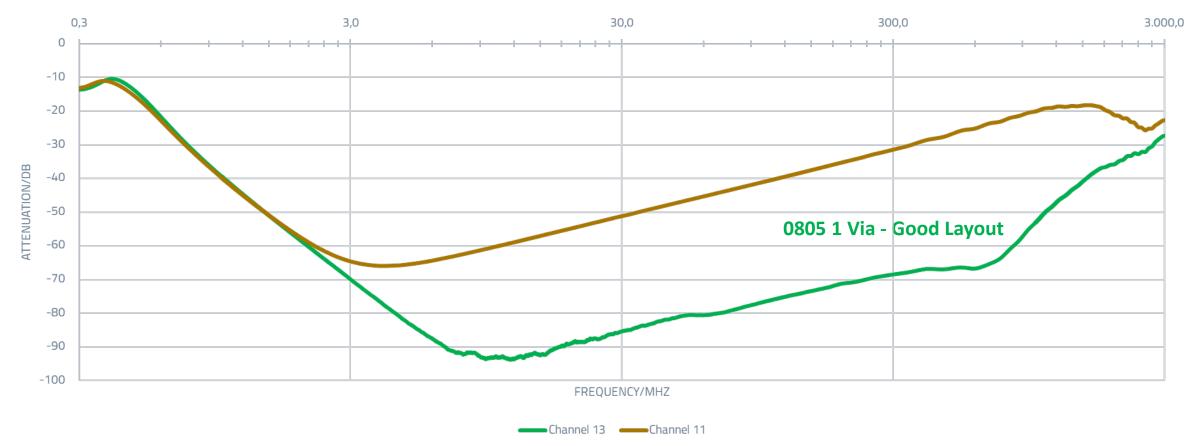

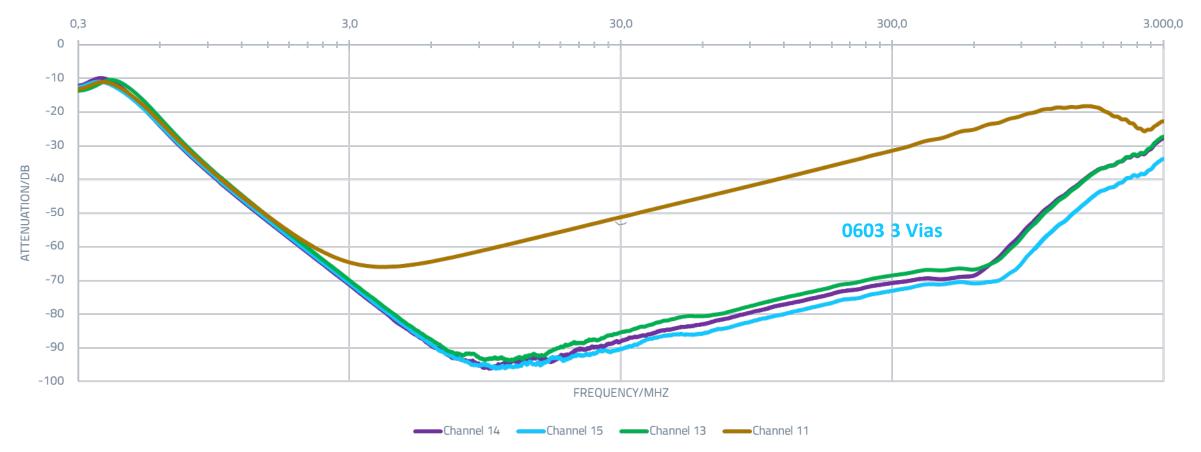

#### S21 Insertion Loss (R&S ZNB20 VNA)

Channel 11

0

Good board realization

#### Measurement of insertion loss in a 90° PLACEMENT design

0

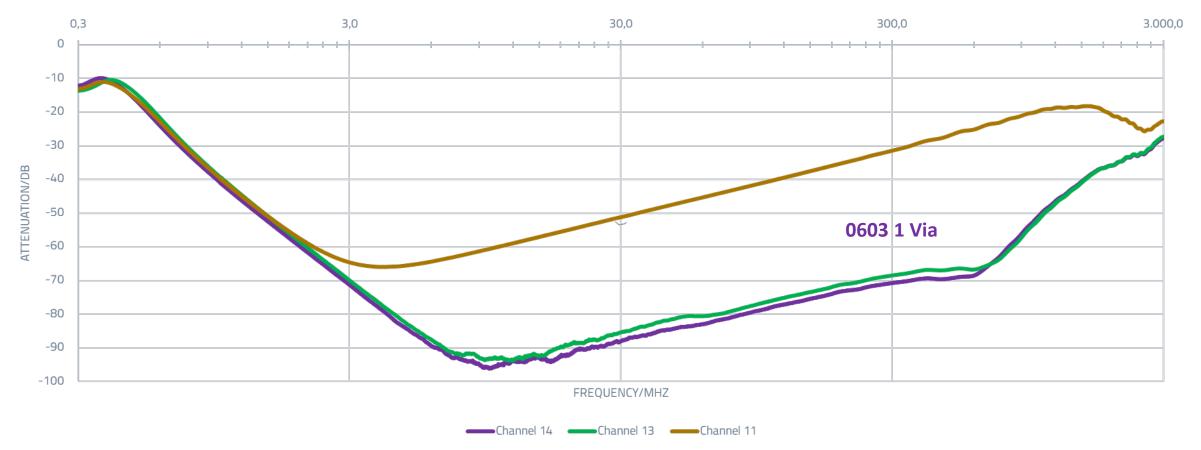

#### S21 Insertion Loss (R&S ZNB20 VNA)

Good board realization with smaller components

#### Measurement of insertion loss in a 90° design

#### S21 Insertion Loss (R&S ZNB20 VNA)

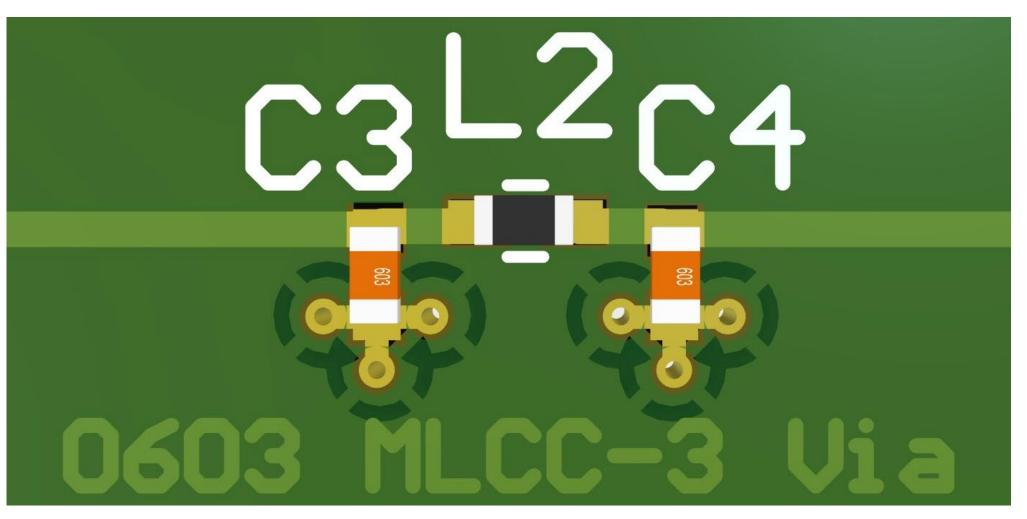

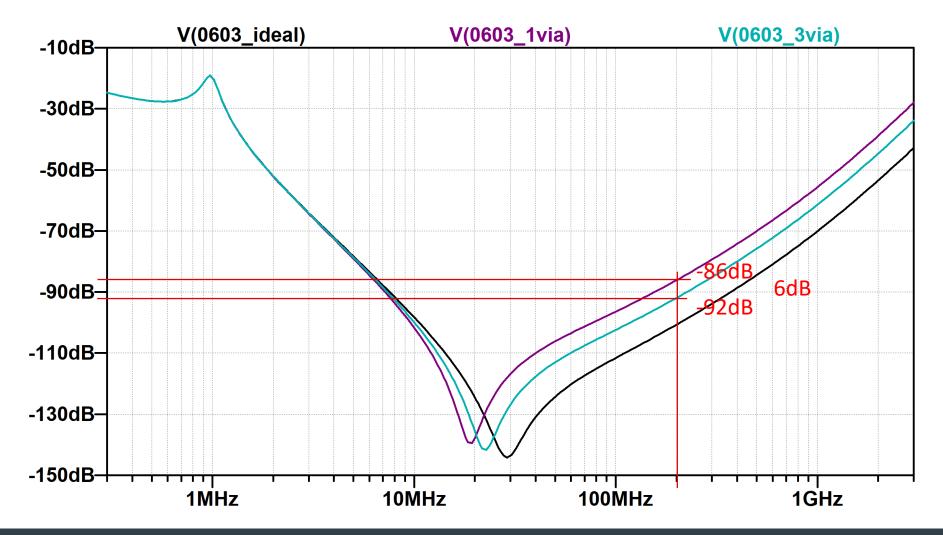

Better board realization with 3 Vias

#### Measurement of insertion loss in a 90° design

0

#### S21 Insertion Loss (R&S ZNB20 VNA)

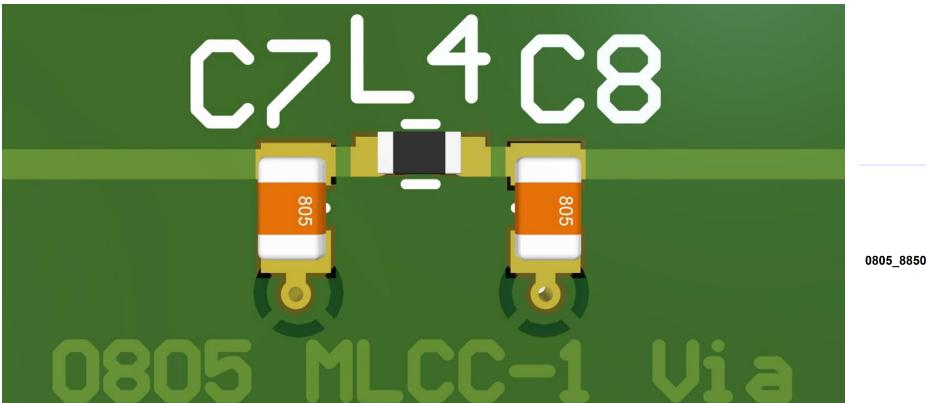

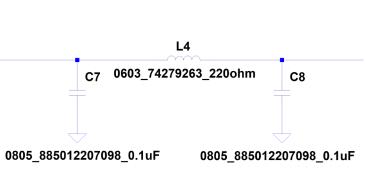

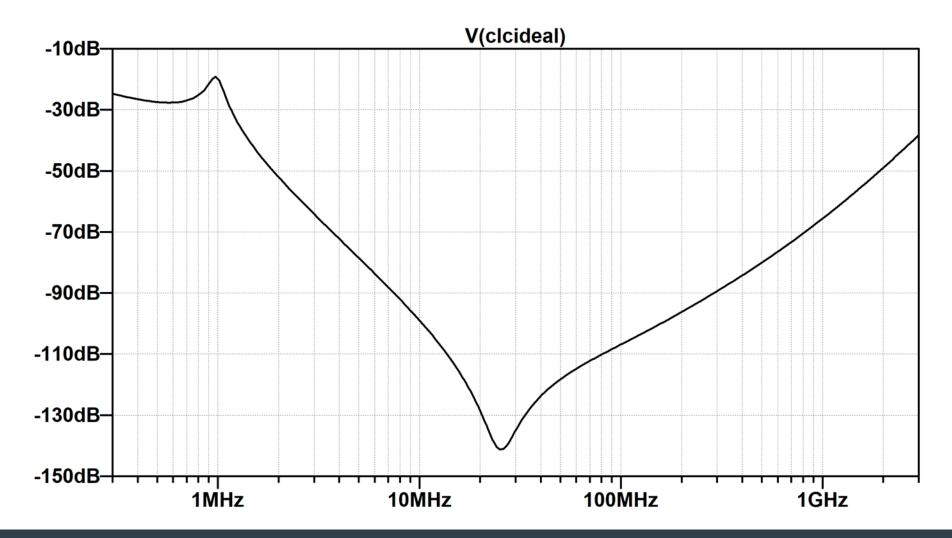

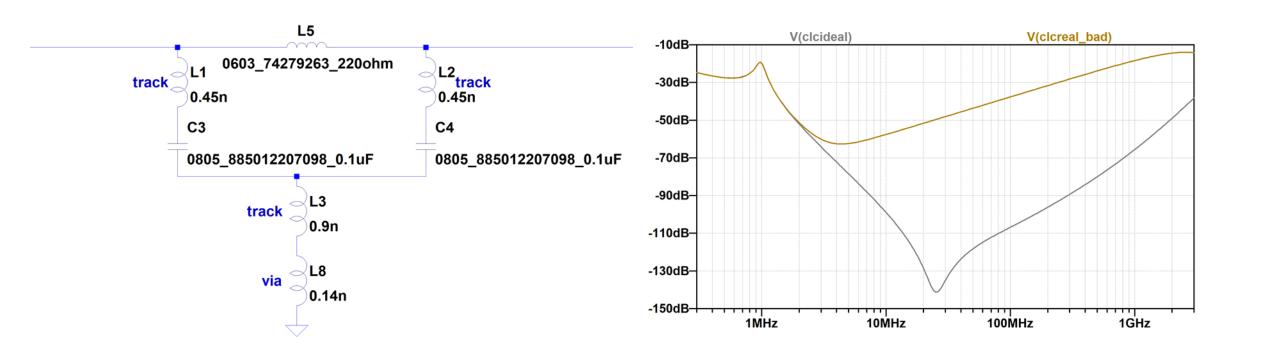

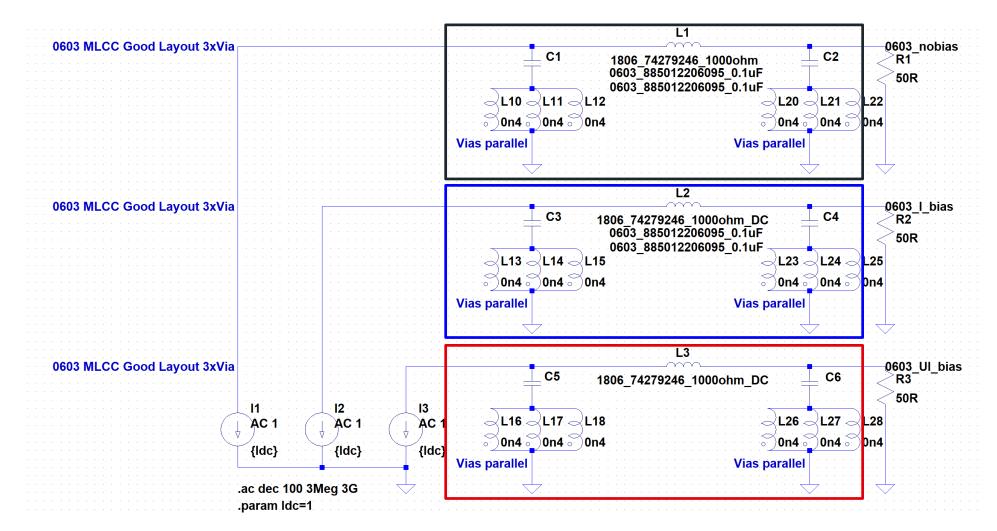

## **PI filter simulation with LTSpice**

Simulation with LTSpice – PI with MLCCs and ferrite, inductances of track/vias

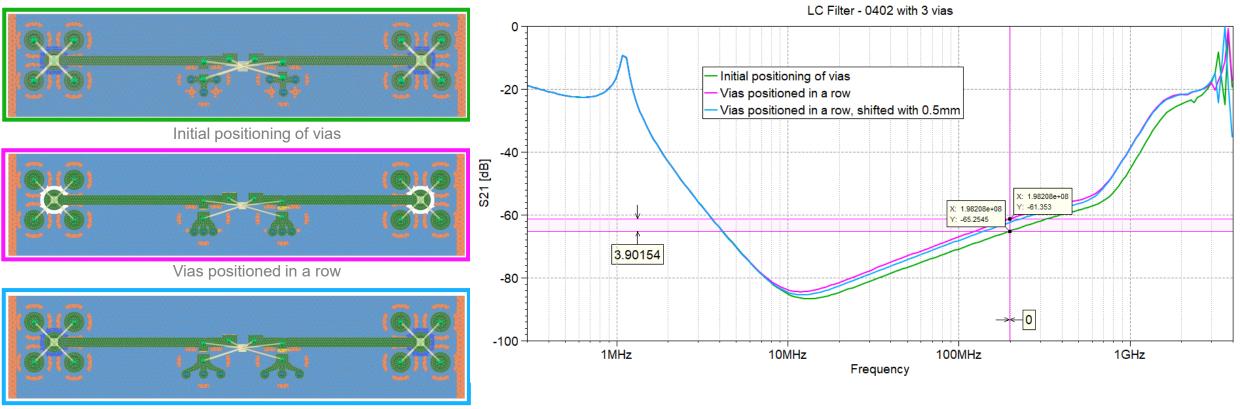

## **Different GND Via Placement**

## **Different GND Via Placement**

EMCOS Simulation show up to 4dB difference

Vias positioned in a row, shifted with 0.5mm

# **BIAS EFFECTS**

Capacitor and ferrite

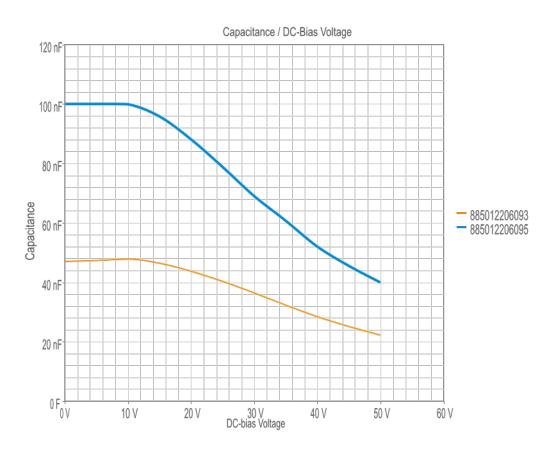

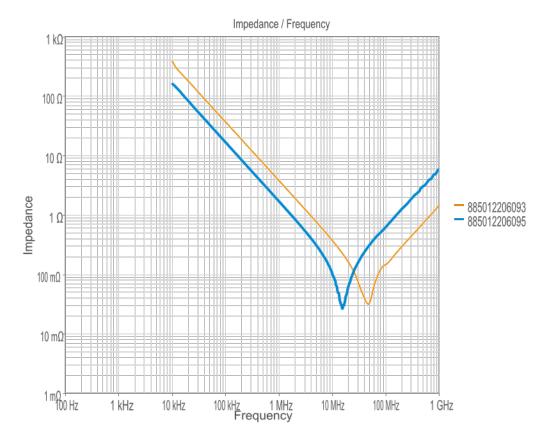

**Capacitor Bias effects**

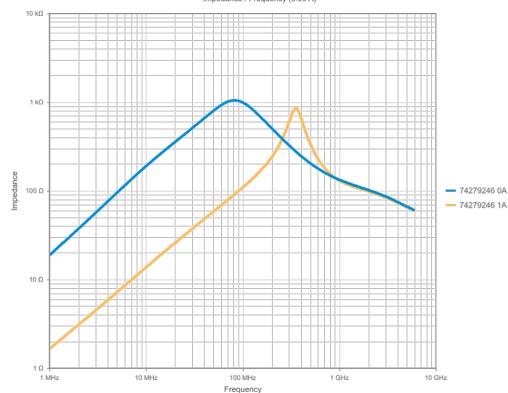

Inductor (ferrite) Bias effects

Equivalent capacitor component for simulation

DC-Bias 885012206095 vs. 885012206093

Impedance 885012206095 vs. 885012206093

#### Behavior of ferrite

Impedance / Frequency (0.00 A)

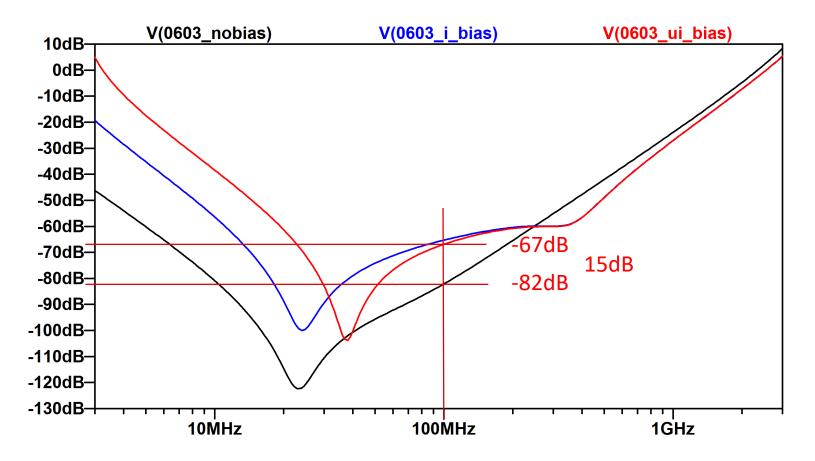

#### Simulation

Simulation results

PI-Filter mit Anbindung zu GND

20