# **Application Note**

# METHOD OF IMPLEMENTATION (MOI) FOR DISPLAYPORT 80 COMPLIANCE TESTS

#### **Products:**

▶ R&S®ZNB

Patrick McKenzie | 1SLXXX | Version 1a | 07.2024

Find the most up-to-date document on our homepage

This document is complemented by configuration files. The configuration files may be updated even if the version of the document remains unchanged.

# **Contents**

| 1                        | Introduction                                                                                              | 3      |

|--------------------------|-----------------------------------------------------------------------------------------------------------|--------|

| 1.1                      | References                                                                                                | 3      |

| 2                        | Required equipment                                                                                        | 4      |

| 2.1                      | R&S®ZNB20 configuration                                                                                   | 4      |

| 3                        | Test overview and preparation                                                                             | 5      |

| 3.1<br>3.2               | Measurement scope Test setup                                                                              |        |

| 3.2.1                    | R&S®ZNB20 test setup                                                                                      | 5      |

| 3.3                      | Necessary software tools                                                                                  | 6      |

| 3.3.1                    | Get_iPar                                                                                                  | 6      |

| 3.4<br>3.5<br>3.6<br>3.7 | Touchstone file naming convention  DisplayPort Alt Mode  Recall setup files  Calibration and de-embedding | 7<br>8 |

| 3.7.1<br>3.7.2           | Coaxial calibration  De-embedding test fixtures                                                           |        |

| 3.8                      | Stimulus rise time adjustment                                                                             | 15     |

| 4                        | Compliance measurements with R&S®ZNB20                                                                    | 16     |

| 4.1                      | Frequency domain tests                                                                                    | 16     |

| 4.1.1                    | Test Procedure                                                                                            | 16     |

| 4.2                      | Time domain tests                                                                                         | 26     |

| 4.2.1                    | Test Procedure                                                                                            | 26     |

# 1 Introduction

The purpose of this document is to provide a step-by-step guidance on how to perform VESA compliance testing on DisplayPort 80 cable assembly.

Throughout this Method of Implementation (MOI), procedures will detail how to perform such VESA compliance testing using the R&S® ZNB lineup of Network Analyzers.

#### 1.1 References

VESA DisplayPort (DP) Standard Version 2.1a 18 December, 2023

VESA DisplayPort v2.1 PHY Layer Compliance Test Specification (PHY CTS) Revision 1.0 12 June, 2023

VESA DisplayPort Alt Mode on USB Type-C Standard (DisplayPort Alt Mode) Version 2.1 02 August, 2024

# 2 Required equipment

# 2.1 R&S®ZNB20 configuration

| Description             | Equipment                                                                                                                                                                                                                                                                             | Quantity                          |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Network analyzer        | R&S®ZNB20 vector network analyzer, 4 ports, 100kHz - 20GHz, PC3.5 connectors with:  — R&S®ZNB-K2, time domain (TDR) analysis (software license)  — R&S®ZNB-K20, extended time domain (TDR) analysis (software license)  — R&S®ZNB-K220, In-situ de-embedding (ISD) (software license) | 1                                 |

| RF cable                | R&S <sup>®</sup> ZV-Z193 var60, 50 Ohm, DC to 26.5GHz, 3.5mm(f)-3.5mm(m), flexible, phase stable, 60 inch (1520mm)                                                                                                                                                                    | 4                                 |

| Calibration unit/kit    | One of the following:  - R&S®ZN-Z52 var30 calibration unit, 100kHz to 26.5 GHz, 4 ports, 3.5mm(f)  - R&S®ZN-Z53 var32 calibration unit, 100 kHz to 26.5 GHz, 2 ports, 3.5mm(f)  - R&S®ZN-Z135 var03 calibration kit, 50 Ohm, 0Hz to 26.5 GHz, 3.5mm(f)                                | 1                                 |

| Receptacle test fixture | Enhanced fsDP: Luxshare-ICT TFDP-V22RA  Enhanced mDP: Luxshare-ICT TFDP-M21RA  USB4 Type-C: Luxshare-ICT TF21-189G                                                                                                                                                                    | A set of each based on cable type |

| 50 Ohm terminator       | One of the following:  — Hirose HRM-601A(52)  — XMA 2003-6110-00  — P1dB P1TR-SAM-26G2W                                                                                                                                                                                               | 16                                |

# 3 Test overview and preparation

## 3.1 Measurement scope

This document focusses on how to perform normative and informative compliance measurements for DisplayPort 80 cable assemblies.

Compliance requirements are categorized into two measurement groups:

- ► Frequency Domain

- ILFitAtNq Frequencies (Normative)

- IRL (Normative)

- Integrated Crosstalk- DP (Normative)

- Differential-to-Common Mode Conversion (Normative)

- Integrated Crosstalk between DP Lanes (Informative)

- Integrated Multi-reflection (Informative)

- ▶ Time Domain

- Differential Impedance Profile (Normative)

- Intra-pair Skew (Normative)

- Inter-pair Skew (Informative)

# 3.2 Test setup

# 3.2.1 R&S®ZNB20 test setup

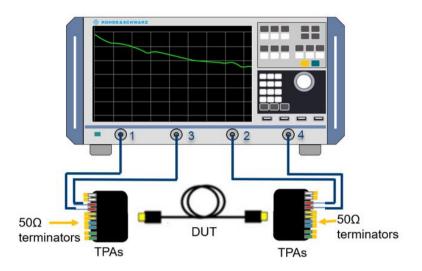

Equipment needed for testing is listed in R&S ZNB20 Configuration. Below is an example setup using the R&S®ZNB20.

To avoid confusion, throughout the document the test fixtures are referred to by their orientation in this diagram (left, right), or simply by an "L" or "R" subscript when appropriate.

## 3.3 Necessary software tools

#### 3.3.1 Get iPar

Several high-speed channel parameters are figures of merit that are calculated from S-parameter data but are not easily determined directly in the VNA firmware interface. VESA provides the Get\_iPar software tool to perform such calculations and provide values for compliance evaluation.

The Get\_iPar tool is freely available at <a href="VESA - GET\_IPAR Tool">VESA - GET\_IPAR Tool</a>

- 1. Download the Get\_iPar file related to DP80.

- 2. Export the contents of the .zip file.

- 3. Install MATLAB Runtime Library R2016a (9.0.1).

# 3.4 Touchstone file naming convention

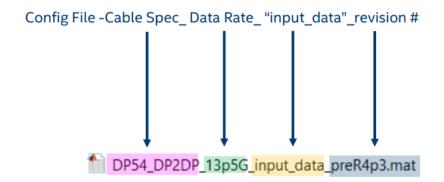

When saving touchstone files (\*.s4p for R&S®ZNB20) to be used with the Get iPAR compliance tools, the following naming convention is recommended:

# 3.5 DisplayPort Alt Mode

DisplayPort Alt Mode is a feature that utilizes the USB Type-C connector on one end of the cable to transmit a DisplayPort signal between a source or sink. The first scenario is using the USB-C portion of the cable on the source side, this is called scenario 2a. The other scenario where the USB-C portion of the cable is connected to the sink side is called scenario 2b. These different scenarios require different cable wiring, more information is below.

#### Scenario 2a Diagram

Scenario 2a Cable Wiring

| Sourc | e Device | Sink [                    | Device                     | Sour | ce Device | Sink De                   | vice                       |

|-------|----------|---------------------------|----------------------------|------|-----------|---------------------------|----------------------------|

| USE   | 3-C pin  | Enhanced DP (normal plug) | Enhanced DP (flipped plug) | US   | SB-C pin  | Enhanced DP (normal plug) | Enhanced DP (flipped plug) |

| A1    | GND      | GND                       | GND                        | B12  | GND       | GND                       | GND                        |

| A2    | Tx1+     | ML2+                      | ML1+                       | B11  | Rx1+      | ML3+                      | ML0+                       |

| A3    | Tx1-     | ML2-                      | ML1-                       | B10  | Rx1-      | ML3-                      | MLO-                       |

| A4    | VBUS     | n/a                       | n/a                        | В9   | VBUS      | n/a                       | n/a                        |

| A5    | CC1      | n/a                       | n/a                        | B8   | SBUS2     | n/a                       | n/a                        |

| A6    | D+       | n/a                       | n/a                        | В7   | D-        | n/a                       | n/a                        |

| A7    | D-       | n/a                       | n/a                        | B6   | D+        | n/a                       | n/a                        |

| A8    | SBUS1    | AUX+                      | AUX-                       | B5   | CC2       | n/a                       | n/a                        |

| A9    | VBUS     | n/a                       | n/a                        | B4   | VBUS      | n/a                       | n/a                        |

| A10   | Rx2-     | ML0-                      | ML3-                       | В3   | Tx2-      | ML1-                      | ML2-                       |

| A11   | Rx2+     | ML0+                      | ML3+                       | B2   | Tx2+      | ML1+                      | ML2+                       |

| A12   | GND      | GND                       | GND                        | B1   | GND       | GND                       | GND                        |

#### Scenario 2b Diagram

Scenario 2b Cable Wiring

| Source Device             |                            | Sink Device |       | Source                    | Sink Device                |     |        |

|---------------------------|----------------------------|-------------|-------|---------------------------|----------------------------|-----|--------|

| Enhanced DP (normal plug) | Enhanced DP (flipped plug) | USB-C pin   |       | Enhanced DP (normal plug) | Enhanced DP (flipped plug) | USB | -C pin |

| GND                       | GND                        | A1          | GND   | GND                       | GND                        | B12 | GND    |

| ML1-                      | ML1-                       | A2          | Tx1+  | ML0-                      | ML0-                       | B11 | Rx1+   |

| ML1+                      | ML1+                       | А3          | Tx1-  | ML0+                      | ML0+                       | B10 | Rx1-   |

| n/a                       | n/a                        | A4          | VBUS  | n/a                       | n/a                        | В9  | VBUS   |

| n/a                       | n/a                        | A5          | CC1   | AUX-                      | AUX+                       | B8  | SBUS2  |

| n/a                       | n/a                        | A6          | D+    | n/a                       | n/a                        | В7  | D-     |

| n/a                       | n/a                        | A7          | D-    | n/a                       | n/a                        | B6  | D+     |

| AUX+                      | AUX-                       | A8          | SBUS1 | n/a                       | n/a                        | B5  | CC2    |

| n/a                       | n/a                        | A9          | VBUS  | n/a                       | n/a                        | B4  | VBUS   |

| ML3+                      | ML3+                       | A10         | Rx2-  | ML2+                      | ML2+                       | В3  | Tx2-   |

| ML3-                      | ML3-                       | A11         | Rx2+  | ML2-                      | ML2-                       | B2  | Tx2+   |

| GND                       | GND                        | A12         | GND   | GND                       | GND                        | B1  | GND    |

# 3.6 Recall setup files

There are recall files delivered together with this document which makes it more convenient to perform the required measurements. There is one recall file for each group of measurements, one additional one for the calibration procedure, and three files for the shielding effectiveness test, e.g., 7 files.

# Recalling the setup files

- 1. On the front panel of the instruments, click the green "PRESET" button.

- 2. Press "FILE" > "Open Recall...".

- 3. Open the recall files (\*.znxml) for the desired tests.

In total there are 5 recall files for the different test groups and another one dedicated for the calibration procedure:

DP80\_Frequency.znxml

- DP80\_Differential\_Impedance\_Profile.znxml

- DP80 Intra-pair Skew.znxml

- DP80\_Inter-pair\_Skew.znxml

Overview about the setting in the different recall files:

| Recall file                               | Start  | Stop   | Step size | IFBW  | Power |

|-------------------------------------------|--------|--------|-----------|-------|-------|

| DP80_Frequency.znxml                      | 10 MHz | 20 GHz | 10 MHz    | 1 kHz | 0 dBm |

| DP80_Differential_Impedance_Profile.znxml | 10 MHz | 20 GHz | 10 MHz    | 1 kHz | 0 dBm |

| DP80_Intra-pair_Skew.znxml                | 10 MHz | 20 GHz | 10 MHz    | 1 kHz | 0 dBm |

| DP80_Inter-pair_Skew.znxml                | 10 MHz | 20 GHz | 10 MHz    | 1 kHz | 0 dBm |

## 3.7 Calibration and de-embedding

Calibration of the VNA and RF cables, as well as de-embedding of the test fixtures, is necessary to accurately measure the cable assembly characteristics at the proper test points.

This is accomplished by performing a coaxial calibration until the end of the RF cables, extract the test fixture S-parameter files using In-situ De-embedding (ISD) technique, and then import de-embedding files in the VNA which removes the effect of the test fixture.

The four different test groups use different frequency ranges. The calibration recall file includes all the required frequency ranges needed for each test group. This allows for all required frequency ranges to be calibrated in a single step.

#### 3.7.1 Coaxial calibration

#### 3.7.1.1 Calibration with automated calibration unit

The most convenient method to perform coaxial calibration is to use an automated calibration unit. Doing so will complete calibration faster and more efficiently.

- 1. Make sure the active setup is the "Calibration" setup.

- 2. On the front panel, press "CAL"

- 3. Select "Start... (Cal Unit)"

4. Select Calibration Type UOSM for best accuracy.

- 5. Follow the calibration wizard during the whole process.

- 6. After the calibration is completed, select "Cal" > "Use Cal".

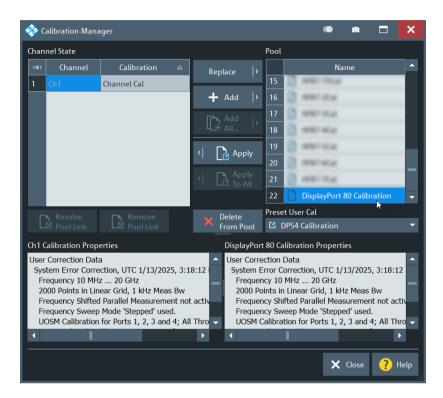

- 7. Enter the "Cal Manager...".

- 8. Add the calibration to the Pool and enter a meaningful name for the calibration.

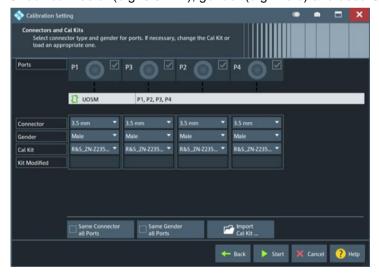

#### 3.7.1.2 Manual calibration with calibration kit

Alternatively, if an automated calibration unit is not available, then a manual calibration kit can be used instead.

- 1. Make sure the active setup is the "Calibration" setup.

- 2. On the front panel, press "CAL" > "Start... (Manual)"

- 3. Select Calibration Type "UOSM" for best accuracy.

4. Open dialog "Calibration Setting".

Check connector (e.g. 3.5 mm), gender (e.g. male) and used CalKit.

5. Start calibration and connect all required calibration standards (open, short, match and unknown through).

It is required to measure at least 3 unknown through connections, however further measured connections will increase the accuracy.

- 6. After the calibration is completed, select "Cal" > "Use Cal".

- 7. Enter the "Cal Manager...".

- 8. Add the calibration to the pool and enter a meaningful name for the calibration.

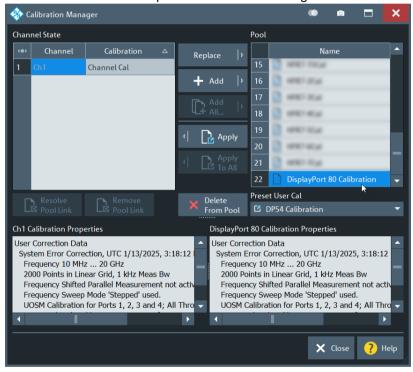

#### 3.7.1.3 Recalling coaxial calibration

After calibrating to the end of the RF cables and storing the calibration data, select the measurement group preset where measurements should be performed. Then recall the calibration in the selected measurement group:

- 1. On the front panel, press "CAL" > "Use Cal".

- 2. Open the "Cal manager ...".

- 3. Click "Apply" to make it active for the current measurement group.

Note: Recalling coaxial calibration procedure must be performed on each measurement group and channel after a firmware preset. Otherwise, measurements will be collected without proper calibration applied, resulting in inaccurate results.

#### 3.7.2 De-embedding test fixtures

After coaxial calibration is completed, the next step is to remove the effect of the test fixtures that will be used during testing. This is accomplished by using files provided by the test fixture supplier or collecting de-embedding files from the fixtures manually. This section describes both methods of deembedding.

The user should verify that the de-embedding files are applied before collecting DUT measurement data. This is especially true after a measurement group preset has been issued. Otherwise, measurements will be collected without proper de-embedding applied, resulting in inaccurate results.

#### 3.7.2.1 Using de-embedding files provided by test fixture supplier

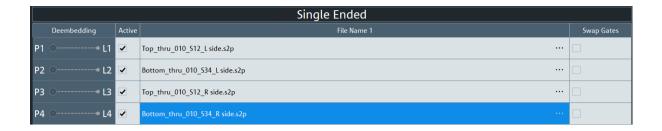

The most convenient de-embedding method is to use files provided by the test fixture vendor.

- 1. On the front panel, press "Offset Embed".

- 2. Select "Single Ended" or "Balanced" depending on the files provided by the fixture vendor.

- 3. Import the 2-port Touchstone files (\*.s2p) or the 4-port Touchstone files (\*.s4p) which are delivered together with the test fixture.

#### 3.7.2.2 Measuring and generating de-embedding files

In case the test fixture vendor could not supply the necessary files for de-embedding, or there is a concern regarding accuracy of such files (from fixture aging/use due to cable insertion over time), the user creates new de-embedding files by making measurements in the VNA firmware. This procedure will use the In-situ de-embedding (ISD) tool which requires the R&S®ZNB-K220 software option.

- 1. Go to Channel > Offset Embed

- 2. Go to Deembed Assistant

- 3. Connect port 1 to '+' on data lane that is under test and port 3 to '-' on data lane that is under test to the left fixture

- 4. Connect port 2 to '+' on data lane that is under test and port 4 to '-' on data lane that is under test to the right fixture

- 5. Select ISD as Fixture Tool

- a) Select "1 x 1 Balanced" for DUT

- b) Select "Balanced" for Left: Model A and Right: Model B

- c) Uncheck "Use same coupon Left and Right"

- d) Press Next

- e) On Coupon A select 1x Open

- f) For Port on Coupon A select "L1"

- g) Click "Measure" for Coupon A

- h) On Coupon B select 1x Open

- i) For Port on Coupon B select "L2"

- j) Click "Measure" for Coupon B

- k) On DUT + Fixture select for left side port "L1" and right side port "L2"

- Connect DUT to fixture left and fixture right.

- m) Click "Measure" DUT + Fixture

- n) Click "Apply"

Fixture de-embedding is now properly applied.

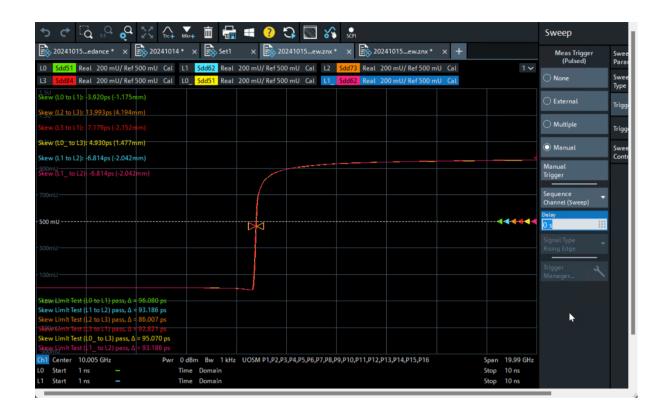

## 3.8 Stimulus rise time adjustment

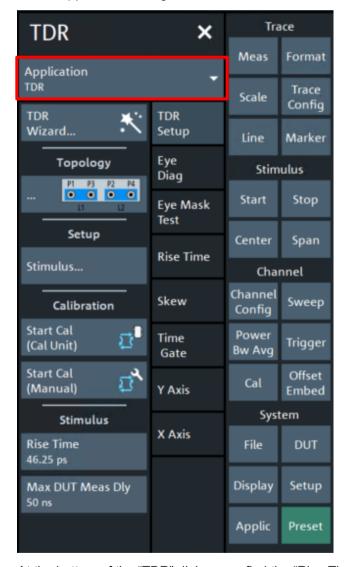

This section demonstrates how the stimulus rise time of the R&S®ZNB is adjusted. This is necessary, when performing the time domain measurements (such as propagation delay), as the VESA requires different rise times be used in each of these scenarios.

*Note*: Licenses for the additional R&S®ZNB-K2 and R&S®ZNB-K20 options will be required for this functionality.

- 1. On the front panel, select "APPLIC".

- In the "Application" dialog, select "TDR".

At the bottom of the "TDR" dialog, you find the "Rise Time" button.

3. Select "Rise Time" to adjust the rise time.

The rise time value can be defined to 10%/90% or 20%/80%.

# 4 Compliance measurements with R&S®ZNB20

This section describes how to perform the compliance measurements with the R&S®ZNB20 4-port vector network analyzer.

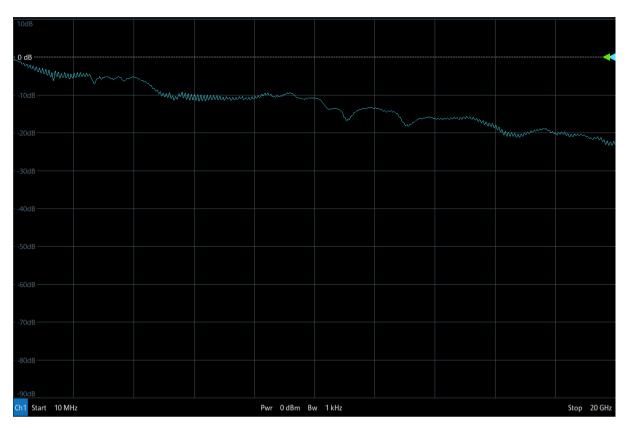

### 4.1 Frequency domain tests

In this group, the following normative tests will be performed:

- ► Insertion Loss Fit at Nyquist Frequencies (ILfitatNq)

- ► Integrated Return Loss (IRL)

- ► Integrated Crosstalk between (IXT\_DP)

- ▶ Differential-to-Common-Mode Conversion (Scd)

In this group, the following informative tests will be performed:

- ► Integrated Crosstalk between DP Lanes (INEXT/IFEXT)

- ► Integrated Multi-reflection (IMR)

#### 4.1.1 Test Procedure

The tests above for DP80 utilize the GetiPar tool. The compliance tool can be downloaded here: VESA - GET\_IPAR Tool

Note: Terminate all unused 3.5mm ports with  $50\Omega$  loads/matches.

Recall the setup file "DP80\_Frequency.znxml"

Note: The normative parameters of interest (ILfitatNq, IMR, etc.) cannot be processed natively in the network analyzer firmware.

- 2. Verify that the calibration and de-embedding data is recalled and enabled

- 3. Perform the measurement and export the Touchstone file.

- a) Using the port mapping defined in the table below for your cable type, connect Port 1, Port 3, Port 2, and Port to the respective test fixture ports.

Connections required for Enhanced DP to Enhanded DP and Enhanced mDP to Enhanced mDP:

| # | Test Item                         | Port 1         | Port 3         | Port 2             | Port 4             | Filename               |

|---|-----------------------------------|----------------|----------------|--------------------|--------------------|------------------------|

| 1 | IL, ML0                           | ML0+ (Left TF) | ML0- (Left TF) | ML0+<br>(Right TF) | ML0-<br>(Right TF) | IL_ML0.s4p             |

| 2 | FEXT, Left<br>ML0 to<br>Right ML1 | ML0+ (Left TF) | ML0- (Left TF) | ML1+<br>(Right TF) | ML1-<br>(Right TF) | FEXTL_ML0_to_R_ML1.s4p |

| 3 | FEXT, Left<br>ML0 to<br>Right ML2 | ML0+ (Left TF) | ML0- (Left TF) | ML2+<br>(Right TF) | ML2-<br>(Right TF) | FEXTL_ML0_to_R_ML2.s4p |

| 4 | FEXT, Left<br>ML0 to<br>Right ML3 | ML0+ (Left TF) | ML0- (Left TF) | ML3+<br>(Right TF) | ML3-<br>(Right TF) | FEXTL_ML0_to_R_ML3.s4p |

| 5 | NEXT, Left<br>ML0 to Left<br>ML1  | ML0+ (Left TF) | ML0- (Left TF) | ML1+<br>(Left TF)  | ML1-<br>(Left TF)  | NEXTL_ML0_to_L_ML1.s4p |

| 6 | NEXT, Left<br>ML0 to Left<br>ML2  | ML0+ (Left TF) | ML0- (Left TF) | ML2+<br>(Left TF)  | ML2-<br>(Left TF)  | NEXTL_ML0_to_L_ML2.s4p |

| #  | Test Item                             | Port 1          | Port 3          | Port 2             | Port 4             | Filename               |

|----|---------------------------------------|-----------------|-----------------|--------------------|--------------------|------------------------|

| 7  | ML0 to Left<br>ML3                    | ML0+ (Left TF)  | ML0- (Left TF)  | ML3+<br>(Left TF)  | ML3-<br>(Left TF)  | NEXTL_ML0_to_L_ML3.s4p |

| 8  | FEXT,<br>Right ML0<br>to Left ML1     | ML0+ (Right TF) | ML0- (Right TF) | ML1+<br>(Left TF)  | ML1-<br>(Left TF)  | FEXTR_ML0_to_L_ML1.s4p |

| 9  | FEXT,<br>Right ML0<br>to Left ML2     | ML0+ (Right TF) | ML0- (Right TF) | ML2+<br>(Left TF)  | ML2-<br>(Left TF)  | FEXTR_ML0_to_L_ML2.s4p |

| 10 | FEXT,<br>Right ML0<br>to Left ML3     | ML0+ (Right TF) | ML0- (Right TF) | ML3+<br>(Left TF)  | ML3-<br>(Left TF)  | FEXTR_ML0_to_L_ML3.s4p |

| 11 | NEXT,<br>Right ML0<br>to Right<br>ML1 | ML0+ (Right TF) | ML0- (Right TF) | ML1+<br>(Right TF) | ML1-<br>(Right TF) | NEXT_R_ML0_toR_ML1.s4p |

| 12 | NEXT,<br>Right ML0<br>to Right<br>ML2 | ML0+ (Right TF) | ML0- (Right TF) | ML2+<br>(Right TF) | ML2-<br>(Right TF) | NEXT_R_ML0_toR_ML2.s4p |

| 13 | NEXT,<br>Right ML0<br>to Right<br>ML3 | ML0+ (Right TF) | ML0- (Right TF) | ML3+<br>(Right TF) | ML3-<br>(Right TF) | NEXT_R_ML0_toR_ML3.s4p |

| 14 | IL, ML1                               | ML1+ (Left TF)  | ML1- (Left TF)  | ML1+<br>(Right TF) | ML1-<br>(Right TF) | IL_ML1.s4p             |

| 15 | FEXT, Left<br>ML1 to<br>Right ML2     | ML1+ (Left TF)  | ML1- (Left TF)  | ML2+<br>(Right TF) | ML2-<br>(Right TF) | FEXTL_ML1_to_R_ML2.s4p |

| 16 | FEXT, Left<br>ML1 to<br>Right ML3     | ML1+ (Left TF)  | ML1- (Left TF)  | ML3+<br>(Right TF) | ML3-<br>(Right TF) | FEXTL_ML1_to_R_ML3.s4p |

| 17 | NEXT, Left<br>ML1 to Left<br>ML2      | ML1+ (Left TF)  | ML1- (Left TF)  | ML2+<br>(Left TF)  | ML2-<br>(Left TF)  | NEXTL_ML1_to_L_ML2.s4p |

| 18 | NEXT, Left<br>ML0 to Left<br>ML2      | ML1+ (Left TF)  | ML1- (Left TF)  | ML3+<br>(Left TF)  | ML3-<br>(Left TF)  | NEXTL_ML1_to_L_ML3.s4p |

| 19 | FEXT,<br>Right ML1<br>to Left ML2     | ML1+ (Right TF) | ML1- (Right TF) | ML2+<br>(Left TF)  | ML2-<br>(Left TF)  | FEXTR_ML1_to_L_ML2.s4p |

| 20 | FEXT,<br>Right ML1<br>to Left ML3     | ML1+ (Right TF) | ML1- (Right TF) | ML3+<br>(Left TF)  | ML3-<br>(Left TF)  | FEXTR_ML1_to_L_ML3.s4p |

| 21 | NEXT,<br>Right ML1<br>to Right<br>ML2 | ML1+ (Right TF) | ML1- (Right TF) | ML2+<br>(Right TF) | ML2-<br>(Right TF) | NEXT_R_ML1_toR_ML2.s4p |

| 22 | NEXT,<br>Right ML1<br>to Right<br>ML3 | ML1+ (Right TF) | ML1- (Right TF) | ML3+<br>(Right TF) | ML3-<br>(Right TF) | NEXT_R_ML1_toR_ML3.s4p |

| 23 | IL, ML2                               | ML2+ (Left TF)  | ML2- (Left TF)  | ML2+<br>(Right TF) | ML2-<br>(Right TF) | IL_ML2.s4p             |

| 24 | FEXT, Left<br>ML2 to<br>Right ML3     | ML2+ (Left TF)  | ML2- (Left TF)  | ML3+<br>(Right TF) | ML3-<br>(Right TF) | FEXTL_ML2_to_R_ML3.s4p |

| 25 | NEXT, Left<br>ML2 to Left<br>ML3      | ML2+ (Left TF)  | ML2- (Left TF)  | ML3+<br>(Left TF)  | ML3-<br>(Left TF)  | NEXTL_ML2_to_L_ML3.s4p |

| #  | Test Item                             | Port 1          | Port 3          | Port 2             | Port 4             | Filename               |

|----|---------------------------------------|-----------------|-----------------|--------------------|--------------------|------------------------|

| 26 | FEXT,<br>Right ML2<br>to Left ML3     | ML2+ (Right TF) | ML2- (Right TF) | ML3+<br>(Left TF)  | ML3-<br>(Left TF)  | FEXTR_ML2_to_L_ML3.s4p |

|    | NEXT,<br>Right ML2<br>to Right<br>ML3 | ML2+ (Right TF) | ML2- (Right TF) | ML3+<br>(Right TF) | ML3-<br>(Right TF) | NEXT_R_ML2_toR_ML3.s4p |

| 28 | IL, ML3                               | ML3+ (Left TF)  | ML3- (Left TF)  | ML3+<br>(Right TF) | ML3-<br>(Right TF) | IL_ML3.s4p             |

## Connections required for DP Alt Mode (USB Type-C to Enhanded DP or Enhanced mDP):

| #  | Test Item                             | Port 1          | Port 3          | Port 2             | Port 4             | Filename                |

|----|---------------------------------------|-----------------|-----------------|--------------------|--------------------|-------------------------|

| 1  | IL, Tx1 to<br>ML2                     | Tx1+ (Left TF)  | Tx1- (Left TF)  | ML2+<br>(Right TF) | ML2-<br>(Right TF) | IL_Tx1_to_ML2.s4p       |

| 2  | FEXT, Left<br>Tx1 to<br>Right ML3     | Tx1+ (Left TF)  | Tx1- (Left TF)  | ML3+<br>(Right TF) | ML3-<br>(Right TF) | FEXTL_Tx1_to_R_ML3.s4p  |

| 3  | FEXT, Left<br>Tx1 to<br>Right ML1     | Tx1+ (Left TF)  | Tx1- (Left TF)  | ML1+<br>(Right TF) | ML1-<br>(Right TF) | FEXTL_Tx1_to_R_ML1.s4p  |

| 4  | FEXT, Left<br>Tx1 to<br>Right ML0     | Tx1+ (Left TF)  | Tx1- (Left TF)  | ML0+<br>(Right TF) | ML0-<br>(Right TF) | FEXTL_Tx1_to_R_ML0.s4p  |

| 5  | NEXT, Left<br>Tx1 to Left<br>Rx1      | Tx1+ (Left TF)  | Tx1- (Left TF)  | Rx1+<br>(Left TF)  | Rx1-<br>(Left TF)  | NEXTL_Tx1_to_L_Rx1.s4p  |

| 6  | NEXT, Left<br>Tx1 to Left<br>Tx2      | Tx1+ (Left TF)  | Tx1- (Left TF)  | Tx2+<br>(Left TF)  | Tx2-<br>(Left TF)  | NEXTL_Tx1_to_L_Tx2.s4p  |

| 7  | NEXT, Left<br>Tx1 to Left<br>Rx1      | Tx1+ (Left TF)  | Tx1- (Left TF)  | Rx1+<br>(Left TF)  | Rx1-<br>(Left TF)  | NEXTL_Tx1_to_L_Rx1.s4p  |

| 8  | FEXT,<br>Right ML0<br>to Left Rx1     | ML2+ (Right TF) | ML2- (Right TF) | Rx1+<br>(Left TF)  | Rx1-<br>(Left TF)  | FEXTR_ML2_to_L_Rx1.s4p  |

| 9  | FEXT,<br>Right ML2<br>to Left Rx2     | ML2+ (Right TF) | ML2- (Right TF) | Tx2+<br>(Left TF)  | Tx2-<br>(Left TF)  | FEXTR_ML2_to_L_Tx2.s4p  |

| 10 | FEXT,<br>Right ML2<br>to Left Rx2     | ML2+ (Right TF) | ML2- (Right TF) | Rx2+<br>(Left TF)  | Rx2-<br>(Left TF)  | FEXTR_ML2_to_L_Rx2.s4p  |

| 11 | NEXT,<br>Right ML2<br>to Right<br>ML3 | ML2+ (Right TF) | ML2- (Right TF) | ML3+<br>(Right TF) | ML3-<br>(Right TF) | NEXT_R_ML2_toR_ML3.s4p  |

| 12 | NEXT,<br>Right ML2<br>to Right<br>ML1 | ML2+ (Right TF) | ML2- (Right TF) | ML1+<br>(Right TF) | ML1-<br>(Right TF) | NEXT_R_ML2_toR_ML1.s4p  |

| 13 | NEXT,<br>Right ML0<br>to Right<br>ML2 | ML2+ (Right TF) | ML2- (Right TF) | ML0+<br>(Right TF) | ML0-<br>(Right TF) | NEXT_R_ML2_toR_ML0.s4p  |

| 14 | IL, Rx1 to<br>ML3                     | Rx1+ (Left TF)  | Rx1- (Left TF)  | ML3+<br>(Right TF) | ML3-<br>(Right TF) | IL_Rx1_to_ML3.s4p       |

| 15 | FEXT, Left<br>Rx1 to<br>Right ML2     | Rx1+ (Left TF)  | Rx1- (Left TF)  | ML1+<br>(Right TF) | ML1-<br>(Right TF) | FEXT_L_Rx1_to_R_ML1.s4p |

| #  | Test Item                             | Port 1          | Port 3          | Port 2             | Port 4             | Filename                |

|----|---------------------------------------|-----------------|-----------------|--------------------|--------------------|-------------------------|

| 16 | FEXT, Left<br>ML1 to<br>Right ML3     | Rx1+ (Left TF)  | Rx1- (Left TF)  | ML0+<br>(Right TF) | ML0-<br>(Right TF) | FEXT_L_Rx1_to_R_ML0.s4p |

| 17 | NEXT, Left<br>Rx1 to Left<br>Tx2      | Rx1+ (Left TF)  | Rx1- (Left TF)  | Tx2+<br>(Left TF)  | Tx2-<br>(Left TF)  | NEXTL_Rx1_to_L_Tx2.s4p  |

| 18 | NEXT, Left<br>Rx1 to Left<br>Rx2      | Rx1+ (Left TF)  | Rx1- (Left TF)  | Rx2+<br>(Left TF)  | Rx2-<br>(Left TF)  | NEXTL_Rx1_to_L_Rx2.s4p  |

| 19 | FEXT,<br>Right ML3<br>to Left Tx2     | ML3+ (Right TF) | ML3- (Right TF) | Tx2+<br>(Left TF)  | Tx2-<br>(Left TF)  | FEXTR_ML3_to_L_Tx2.s4p  |

| 20 | FEXT,<br>Right ML3<br>to Left Rx2     | ML3+ (Right TF) | ML3- (Right TF) | Rx2+<br>(Left TF)  | Rx2-<br>(Left TF)  | FEXTR_ML3_to_L_Rx2.s4p  |

| 21 | NEXT,<br>Right ML3<br>to Right<br>ML1 | ML3+ (Right TF) | ML3- (Right TF) | ML1+<br>(Right TF) | ML1-<br>(Right TF) | NEXT_R_ML3_toR_ML1.s4p  |

| 22 | NEXT,<br>Right ML3<br>to Right<br>ML0 | ML3+ (Right TF) | ML3- (Right TF) | ML0+<br>(Right TF) | ML0-<br>(Right TF) | NEXT_R_ML3_toR_ML0.s4p  |

| 23 | IL, Tx2 to<br>ML1                     | Tx2+ (Left TF)  | Tx2- (Left TF)  | ML1+<br>(Right TF) | ML1-<br>(Right TF) | IL_Tx2_to_ML1.s4p       |

| 24 | FEXT, Left<br>Tx2 to<br>Right ML0     | Tx2+ (Left TF)  | Tx2- (Left TF)  | ML0+<br>(Right TF) | ML0-<br>(Right TF) | FEXTL_Tx2_to_R_ML0.s4p  |

| 25 | NEXT, Left<br>Tx2 to Left<br>Rx2      | Tx2+ (Left TF)  | Tx2- (Left TF)  | Rx2+<br>(Left TF)  | Rx2-<br>(Left TF)  | NEXTL_Tx2_to_L_Rx2.s4p  |

| 26 | FEXT,<br>Right ML1<br>to Left Rx2     | ML1+ (Right TF) | ML1- (Right TF) | Rx2+<br>(Left TF)  | Rx2-<br>(Left TF)  | FEXTR_ML1_to_L_Rx2.s4p  |

| 27 | NEXT,<br>Right ML1<br>to Right<br>ML0 | ML1+ (Right TF) | ML1- (Right TF) | ML0+<br>(Right TF) | ML0-<br>(Right TF) | NEXT_R_ML1_toR_ML0.s4p  |

| 28 | IL, Rx2 to<br>ML0                     | Rx2+ (Left TF)  | Rx2- (Left TF)  | ML0+<br>(Right TF) | ML0-<br>(Right TF) | IL_Rx2_to_ML0.s4p       |

- b) After an acquisition is complete, select "FILE" on the front panel then Select "Trace Data" > "s4p Port 1,2,3,4...".

- c) Use the name listed in the 'Filename' column (based on the naming described in 3.4 Touchstone file naming convention) in the above table for the file name of the exported Touchstone file.

- 4. Repeat step 3.a through 3.c for all 28 measurements.

- 5. Import the 28 4-port Touchstone files (\*.s4p) to the "Get\_iPar" software.

The Get\_iPar software can be used for the evaluation of several different compliance requirements. Due to its flexibility, there are configuration files (\*.xlsx) used to automate the post-

processing and evaluation of the cable assembly data. These files needed to be edited to properly perform the interested analysis.

- a) After downloading the Get\_iPar files, described in 3.3.1 Get\_iPar, extract the content of the .zip file.

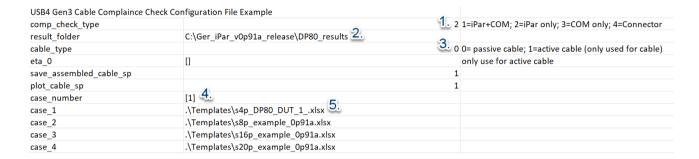

- b) Within the 'Templates' folder there is a file called 'USB4\_Gen3\_CableCom\_Config\_Example.xlsx'. This file will be used in the following steps, but must first be modified to reflect the settings necessary for VESA DP80 passive cable assembly testing. Modify the file as shown below:

- 1. select iPar only by typing '2' into column b of the config excel sheet

- 2. Copy in the folder directory you would like the results to be put in after the compliance test has been completed

- 3. Select '0' for passive cable in column b of the config excel sheet

- 4. Select the option that applies to your measurement data, in this example, we are showing data captured with a 4 port VNA, so we are selecting the s4p case. Note, the Get\_iPar tool supports s4p, s8p, s16p, and s20p files.

- 5. Ensure that the case information in column b points to the excel file that contains a list of all s4p files that were measured for your DUT.

- c) After editing 'USB4\_Gen3\_CableCom\_Config\_Example.xlsx' is completed. Open the file titled 's4p\_example\_0p91a.xlsx' this excel sheet will contain the name of each of the 28 s4p files captured for the compliance test. Ensure all 28 s4p files are in the same file directory as the 's4p\_example\_0p91a.xlsx' file.

| folder     | C:\Cable_Tools\measured_sp_examples\s4p\ |            |               |

|------------|------------------------------------------|------------|---------------|

| VNA_port   | 4                                        |            |               |

| sp_file_1  | IL_ML0.s4p                               | sp_port_1  | [1 2 3 4]     |

| sp_file_2  | FEXTL_ML0_to_R_ML1.s4p                   | sp_port_2  | [1638]        |

| sp_file_3  | FEXTL_ML0_to_R_ML2.s4p                   | sp_port_3  | [1 10 3 12]   |

| sp_file_4  | FEXTL_MLO_to_R_ML3.s4p                   | sp_port_4  | [1 14 3 16]   |

| sp_file_5  | NEXTL_ML0_to_L_ML1.s4p                   | sp_port_5  | [1537]        |

| sp_file_6  | NEXTL_ML0_to_L_ML2.s4p                   | sp_port_6  | [19311]       |

| sp_file_7  | NEXTL_ML0_to_L_ML3.s4p                   | sp_port_7  | [1 13 3 15]   |

| sp_file_8  | FEXTR_ML0_to_L_ML1.s4p                   | sp_port_8  | [2 5 4 7]     |

| sp_file_9  | FEXTR_ML0_to_L_ML2.s4p                   | sp_port_9  | [2 9 4 11]    |

| sp_file_10 | FEXTR_ML0_to_L_ML3.s4p                   | sp_port_10 | [2 13 4 15]   |

| sp_file_11 | NEXT_R_ML0_toR_ML1.s4p                   | sp_port_11 | [2 6 4 8]     |

| sp_file_12 | NEXT_R_ML0_toR_ML2.s4p                   | sp_port_12 | [2 10 4 12]   |

| sp_file_13 | NEXT_R_ML0_toR_ML3.s4p                   | sp_port_13 | [2 14 4 16]   |

| sp_file_14 | IL_ML1.s4p                               | sp_port_14 | [5 6 7 8]     |

| sp_file_15 | FEXTL_ML1_to_R_ML2.s4p                   | sp_port_15 | [5 10 7 12]   |

| sp_file_16 | FEXTL_ML1_to_R_ML3.s4p                   | sp_port_16 | [5 14 7 16]   |

| sp_file_17 | NEXTL_ML1_to_L_ML2.s4p                   | sp_port_17 | [5 9 7 11]    |

| sp_file_18 | NEXTL_ML1_to_L_ML3.s4p                   | sp_port_18 | [5 13 7 15]   |

| sp_file_19 | FEXTR_ML1_to_L_ML2.s4p                   | sp_port_19 | [6 9 8 11]    |

| sp_file_20 | FEXTR_ML1_to_L_ML3.s4p                   | sp_port_20 | [6 13 8 15]   |

| sp_file_21 | NEXT R ML1 to R ML2.s4p                  | sp_port_21 | [6 10 8 12]   |

| sp_file_22 | NEXT_R_ML1_toR_ML3.s4p                   | sp_port_22 | [6 14 8 16]   |

| sp_file_23 | IL_ML2.s4p                               | sp_port_23 | [9 10 11 12]  |

| sp_file_24 | FEXT_L_ML2_to_R_ML3.s4p                  | sp_port_24 | [9 14 11 16]  |

| sp_file_25 | NEXTL_ML2_to_L_ML3.s4p                   | sp_port_25 | [9 13 11 15]  |

| sp_file_26 | FEXT_R_ML2_to_L_ML3.s4p                  | sp_port_26 | [10 13 12 15] |

| sp_file_27 | NEXT_R_ML2_toR_ML3.s4p                   | sp_port_27 | [10 14 12 16] |

| sp_file_28 | IL_ML3.s4p                               | sp_port_28 | [13 14 15 16] |

After the 28 port names are listed in the excel file there will be an additional 16 USB2 files, these can be replaced with a closed square bracket like this: '[]' the closed square brackets indicate to the tool that this will not be tested, if the square brackets are not there then the get\_iPar tool will not work.

|              | <br>1        | 1_            |

|--------------|--------------|---------------|

| usb2_file_1  | usb2_port_1  | [17 1 19 3 ]  |

| usb2_file_2  | usb2_port_2  | [17 2 19 4]   |

| usb2_file_3  | usb2_port_3  | [17 5 19 7]   |

| usb2_file_4  | usb2_port_4  | [17 6 19 8]   |

| usb2_file_5  | usb2_port_5  | [17 9 19 11]  |

| usb2_file_6  | usb2_port_6  | [17 10 19 12] |

| usb2_file_7  | usb2_port_7  | [17 13 19 15] |

| usb2_file_8  | usb2_port_8  | [17 14 19 16] |

| usb2_file_9  | usb2_port_9  | [18 1 20 3 ]  |

| usb2_file_10 | usb2_port_10 | [18 2 20 4]   |

| usb2_file_11 | usb2_port_11 | [18 5 20 7]   |

| usb2_file_12 | usb2_port_12 | [18 6 20 8]   |

| usb2_file_13 | usb2_port_13 | [18 9 20 11]  |

| usb2_file_14 | usb2_port_14 | [18 10 20 12] |

| usb2_file_15 | usb2_port_15 | [18 13 20 15] |

| usb2_file_16 | usb2_port_16 | [18 14 20 16] |

d) Ensure that the correct limits for the Get\_iPar tool are set, to do this go to the 'data' folder in the Get\_iPar\_v0p91a\_release and put in the following files downloaded from VESA website:

| DP80_DP2DP_20G_input_data_R3.mat | <b>②</b> | 10/24/2021 9:29 PM  | Microsoft Access Tabl | 31,041 KB |

|----------------------------------|----------|---------------------|-----------------------|-----------|

| DP80_DP2TC_20G_input_data_R3.mat | •        | 10/24/2021 11:17 PM | Microsoft Access Tabl | 31,041 KB |

| input_data.mat                   | <b>②</b> | 12/19/2019 1:27 PM  | Microsoft Access Tabl | 31,041 KB |

These files set the correct limits for the Get\_iPar tool to determine the correct pass/fail criteria. These are downloadable on the VESA site here

To enable the DP2DP or DP2TC(Type-C) for Alt mode testing you need to rename the file to 'input\_data.mat'

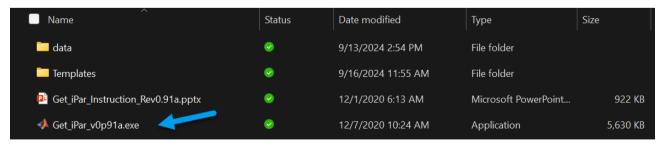

e) Navigate to the root directory of the extracted Get\_iPar files, and run the \*.exe

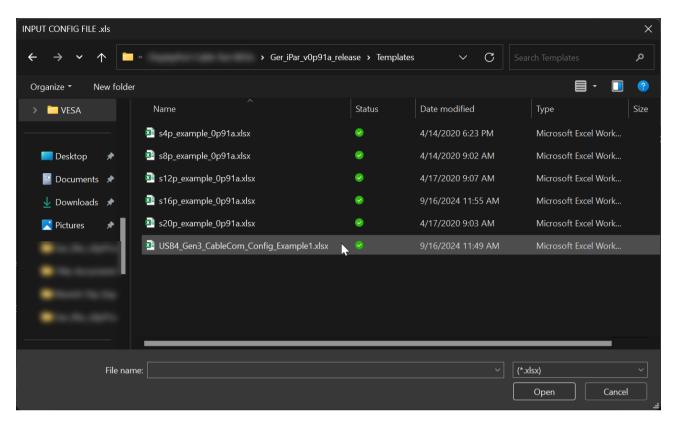

f) Next, a pop-up window will appear, titled "INPUT CONFIG FILE". Select the 'USB4\_Gen3\_CableCom\_Config\_Example.xlsx" file in the 'Templates' folder.

- g) The Get\_iPar software will begin processing the 28 Touchstone files. This process may take several minutes. Plots will appear on the screen, but will automatically close. These can be viewed in the file location you specified the results would be placed in step b.

- 6. Retrieve the analysis results from the software.

Once the Get\_iPar software has completed it's analysis, the compliance results will be stored in two spreadsheets within the folder outlined you designated in step b. The spreadsheets include numerical values as well as pass or fail judgement against the respective limit.

| Passive cable        | TX1(L)      | TX1(R)       | RX1(L) | RX1(R) | TX2(L) | TX2(R) | RX2(L) | RX2(R) | Limit  | Pass/Fail |

|----------------------|-------------|--------------|--------|--------|--------|--------|--------|--------|--------|-----------|

| ILfit@0.1GHz, dB     | -0.67       | -0.67        | -0.67  | -0.67  | -0.65  | -0.65  | -0.66  | -0.66  | -1     | Pass      |

| ILfit@2.7GHz, dB     | -3.33       | -3.33        | -3.26  | -3.26  | -3.25  | -3.25  | -3.36  | -3.36  | -4     | Pass      |

| ILfit@5GHz, dB       | -4.39       | -4.39        | -4.38  | -4.38  | -4.37  | -4.37  | -4.44  | -4.44  | -5.5   | Pass      |

| ILfit@6.75GHz, dB    | -5.05       | -5.05        | -5.11  | -5.11  | -5.12  | -5.12  | -5.15  | -5.15  | -6.5   | Pass      |

| ILfit@10GHz, dB      | -6.41       | -6.41        | -6.57  | -6.57  | -6.64  | -6.64  | -6.69  | -6.69  | -8.5   | Pass      |

| ILfit@15GHz, dB      | -9.67       | -9.67        | -9.72  | -9.72  | -10    | -10    | -10.35 | -10.35 | -13    | Pass      |

| IMR, dB              | -38.95      | -38.95       | -39.79 | -39.79 | -40.33 | -40.33 | -38    | -38    | -30.9  | Pass      |

| IRL, dB              | -20.46      | -20.46       | -20.05 | -20.05 | -19.34 | -19.34 | -21.12 | -21.12 | -16.64 | Pass      |

| C2D, dB              | -22.11      | -27.9        | -22.25 | -24.5  | -24.87 | -23.22 | -20.53 | -21.29 | -17    | Pass      |

| D2C, dB              | -22.08      | -28.04       | -22.6  | -24.21 | -24.7  | -23.27 | -20.63 | -21.26 | -17    | Pass      |

| IXT_DP, dB           | -41.01      | -43.15       | -41.6  | -39.54 | -39.9  | -40.82 | -41.56 | -41.05 | -34.9  | Pass      |

| IXT_USB, dB          | -31.23      | -32.18       | -28.88 | -29.44 | -29.53 | -29.12 | -32.34 | -31.55 | -36    | Fail      |

| Detailed crosstalk b | etween ea   | ch pair in d | В      |        |        |        |        |        |        |           |

| Vic/Agg Port         | TX1(L)      | TX1(R)       | RX1(L) | RX1(R) | TX2(L) | TX2(R) | RX2(L) | RX2(R) |        |           |

| TX1(L)               |             |              | -31.49 | -43.55 | -47.12 | -45.62 | -47.76 | -51.12 |        |           |

| TX1(R)               |             |              | -47    | -32.34 | -48.73 | -46.35 | -48.23 | -50.79 |        |           |

| RX1(L)               | -31.49      | -47          |        |        | -32.49 | -45.36 | -45.62 | -46.96 |        |           |

| RX1(R)               | -43.55      | -32.34       |        |        | -44.16 | -32.79 | -45.45 | -46.88 |        |           |

| TX2(L)               | -47.12      | -48.73       | -32.49 | -44.16 |        |        | -32.69 | -42.96 |        |           |

| TX2(R)               | -45.62      | -46.35       | -45.36 | -32.79 |        |        | -45.79 | -31.73 |        |           |

| RX2(L)               | -47.76      | -48.23       | -45.62 | -45.45 | -32.69 | -45.79 |        |        |        |           |

| RX2(R)               | -51.12      | -50.79       | -46.96 | -46.88 | -42.96 | -31.73 |        |        |        |           |

| USB4 Gen3 Get_iP     | ar Revision | 0.91a        |        |        |        |        |        |        |        |           |

| Report Time: 15-O    | ct-2024 09: | 47:20        |        |        |        |        |        |        |        |           |

#### 4.2 Time domain tests

Time domain measurements are directly performed on the R&S®ZNB20 vector network analyzer. Only for this section the R&S®ZNB-K2 time domain option is required:

In this section, the following normative tests will be performed:

- ▶ Differential Impedance Profile

- Intra-pair Skew

In this section, the following informative tests will be performed:

► Inter-pair Skew

#### 4.2.1 Test Procedure

#### 4.2.1.1 Differential Impedance Profile (Normative)

1. Recall the setup file "DP80\_DP\_Differential\_Impedance\_Profile.znxml" or "DP80\_DP\_Alt\_Mode\_Differential\_Impedance\_Profile.znxml"

Connect DUT to VNA DP2.1 cable

| Port 1         | Port 3         | Port 2             | Port 4             |

|----------------|----------------|--------------------|--------------------|

| ML0+ (Left TF) | ML0- (Left TF) | ML0+<br>(Right TF) | ML0-<br>(Right TF) |

| ML1+ (Left TF) | ML1- (Left TF) | ML1+<br>(Right TF) | ML1-<br>(Right TF) |

| ML2+ (Left TF) | ML2- (Left TF) | ML2+<br>(Right TF) | ML2-<br>(Right TF) |

| ML3+ (Left TF) | ML3- (Left TF) | ML3+<br>(Right TF) | ML3-<br>(Right TF) |

#### DP Alt Mode (Type-C to Enhanced DP or Enhanced mDP)

| Port 1         | Port 3         | Port 2             | Port 4             |

|----------------|----------------|--------------------|--------------------|

| Tx1+ (Left TF) | Tx1- (Left TF) | ML2+<br>(Right TF) | ML2-<br>(Right TF) |

| Rx1+ (Left TF) | Rx1- (Left TF) | ML3+<br>(Right TF) | ML3-<br>(Right TF) |

| Tx2+ (Left TF) | Tx2- (Left TF) | ML1+<br>(Right TF) | ML1-<br>(Right TF) |

| Rx2+ (Left TF) | Rx2- (Left TF) | ML0+<br>(Right TF) | ML0-<br>(Right TF) |

#### DP Alt Mode (Enhanced DP or Enhanced mDP to Type-C)

| Port 1         | Port 3         | Port 2             | Port 4             |

|----------------|----------------|--------------------|--------------------|

| ML0+ (Left TF) | ML0- (Left TF) | Rx1+<br>(Right TF) | Rx1-<br>(Right TF) |

| ML1+ (Left TF) | ML1- (Left TF) | Tx1+<br>(Right TF) | Tx1-<br>(Right TF) |

| ML2+ (Left TF) | ML2- (Left TF) | Tx2+<br>(Right TF) | Tx2-<br>(Right TF) |

| ML3+ (Left TF) | ML3- (Left TF) | Rx2+<br>(Right TF) | Rx2-<br>(Right TF) |

- 3. Verify that the calibration and de-embedding data are recalled and enabled

- 4. Ensure you select correct setup file for the DUT type

- a) DP2.1 cable limits

| Segment                         | Differential<br>Impedance<br>Value | Maximum<br>Tolerance | Comment                                                           |

|---------------------------------|------------------------------------|----------------------|-------------------------------------------------------------------|

| Fixture                         | 100 Ω                              | ±5 Ω                 | Fixture shall be de-embedded during measurement                   |

| Connector                       | 85 Ω                               | ±10 Ω                |                                                                   |

| Paddle Card and Wire Management | 85 Ω                               | ±10 Ω                | Measurements to be made from 20% to 80% with a rise time of 25 ps |

| Cable                           | 85 Ω                               | ±5 Ω                 |                                                                   |

b) DP Alt Mode (Type-C to Enhanced DP or Enhanced mDP) cable limits

| Segment                  | Differential<br>Impedance<br>Value | Maximum<br>Tolerance | Comment                                         |

|--------------------------|------------------------------------|----------------------|-------------------------------------------------|

| Fixture                  | 100 Ω                              | ±5 Ω                 | Fixture shall be de-embedded during measurement |

| USB Type-C<br>Connector  | 85 Ω                               | ±9 Ω                 | Measurements are to be made from                |

| USB Type-C Bulk<br>Cable | 85 Ω                               | ±5 Ω                 | 20% to 80% with a rise time of 25 ps            |

- 5. If the trace falls out of the limit lines defined in the setup file for your DUT, then fail

- 6. Repeat steps 2 through 4 for each connection for the given DUT

#### 4.2.1.2 Intra-pair Skew (Normative)

1. Recall the setup file "DP80\_Intra-pair\_Skew.znxml"

Connect DUT to VNA DP cable

| Port 1         | Port 3         | Port 2             | Port 4             |

|----------------|----------------|--------------------|--------------------|

| ML0+ (Left TF) | ML0- (Left TF) | ML0+<br>(Right TF) | ML0-<br>(Right TF) |

| ML1+ (Left TF) | ML1- (Left TF) | ML1+<br>(Right TF) | ML1-<br>(Right TF) |

| ML2+ (Left TF) | ML2- (Left TF) | ML2+<br>(Right TF) | ML2-<br>(Right TF) |

| ML3+ (Left TF) | ML3- (Left TF) | ML3+<br>(Right TF) | ML3-<br>(Right TF) |

#### DP Alt Mode (Type-C to Enhanced DP or Enhanced mDP)

| Port 1         | Port 3         | Port 2             | Port 4             |

|----------------|----------------|--------------------|--------------------|

| Tx1+ (Left TF) | Tx1- (Left TF) | ML2+<br>(Right TF) | ML2-<br>(Right TF) |

| Rx1+ (Left TF) | Rx1- (Left TF) | ML3+<br>(Right TF) | ML3-<br>(Right TF) |

| Tx2+ (Left TF) | Tx2- (Left TF) | ML1+<br>(Right TF) | ML1-<br>(Right TF) |

| Rx2+ (Left TF) | Rx2- (Left TF) | ML0+<br>(Right TF) | ML0-<br>(Right TF) |

#### DP Alt Mode (Enhanced DP or Enhanced mDP to Type-C)

| Port 1         | Port 3         | Port 2             | Port 4             |

|----------------|----------------|--------------------|--------------------|

| ML0+ (Left TF) | ML0- (Left TF) | Rx1+<br>(Right TF) | Rx1-<br>(Right TF) |

| ML1+ (Left TF) | ML1- (Left TF) | Tx1+<br>(Right TF) | Tx1-<br>(Right TF) |

| ML2+ (Left TF) | ML2- (Left TF) | Tx2+<br>(Right TF) | Tx2-<br>(Right TF) |

| ML3+ (Left TF) | ML3- (Left TF) | Rx2+<br>(Right TF) | Rx2-<br>(Right TF) |

- 3. Verify that the calibration and de-embedding data are recalled and enabled

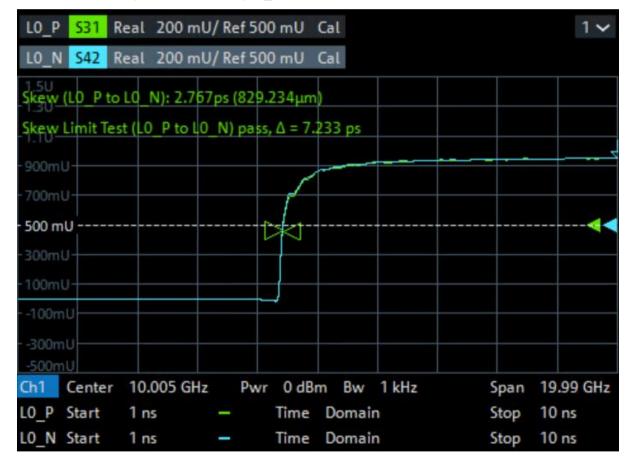

- 4. Evaluate the time delta

- a) DP80 cable: Pass if time is ≤ 10 ps, otherwise fail. While using 25ps (20% to 80%) rise time

- b) DP Alt Mode: Pass if time is < 30 ps, otherwise fail. While using 50ps (20% to 80%) rise time

- 5. Repeat steps 2 through 4 for each connection for the given DUT

#### 4.2.1.3 Inter-pair Skew (Informative)

1. Recall the setup file "DP80\_Inter-pair\_Skew.znxml"

#### 2. Connect DUT to VNA

#### DP cable

| Port 1         | Port 3         | Port 2             | Port 4             |

|----------------|----------------|--------------------|--------------------|

| ML0+ (Left TF) | ML0- (Left TF) | ML0+<br>(Right TF) | ML0-<br>(Right TF) |

| ML1+ (Left TF) | ML1- (Left TF) | ML1+<br>(Right TF) | ML1-<br>(Right TF) |

| ML2+ (Left TF) | ML2- (Left TF) | ML2+<br>(Right TF) | ML2-<br>(Right TF) |

| ML3+ (Left TF) | ML3- (Left TF) | ML3+<br>(Right TF) | ML3-<br>(Right TF) |

#### DP Alt Mode (Type-C to Enhanced DP or Enhanced mDP)

| Port 1         | Port 3         | Port 2             | Port 4             |

|----------------|----------------|--------------------|--------------------|

| Tx1+ (Left TF) | Tx1- (Left TF) | ML2+<br>(Right TF) | ML2-<br>(Right TF) |

| Rx1+ (Left TF) | Rx1- (Left TF) | ML3+<br>(Right TF) | ML3-<br>(Right TF) |

| Tx2+ (Left TF) | Tx2- (Left TF) | ML1+<br>(Right TF) | ML1-<br>(Right TF) |

| Rx2+ (Left TF) | Rx2- (Left TF) | ML0+<br>(Right TF) | ML0-<br>(Right TF) |

DP Alt Mode (Enhanced DP or Enhanced mDP to Type-C)

| Port 1         | Port 3         | Port 2             | Port 4             |

|----------------|----------------|--------------------|--------------------|

| ML0+ (Left TF) | ML0- (Left TF) | Rx1+<br>(Right TF) | Rx1-<br>(Right TF) |

| ML1+ (Left TF) | ML1- (Left TF) | Tx1+<br>(Right TF) | Tx1-<br>(Right TF) |

| ML2+ (Left TF) | ML2- (Left TF) | Tx2+<br>(Right TF) | Tx2-<br>(Right TF) |

| ML3+ (Left TF) | ML3- (Left TF) | Rx2+<br>(Right TF) | Rx2-<br>(Right TF) |

- 3. Verify that the calibration and de-embedding data are recalled and enabled

- 4. Evaluate the time delta (limit is 2UI, which is equivalent to 100ps)

- a) DP2.1 cable: Pass if time is < 100 ps, otherwise fail. While using 25ps (20% to 80%) rise time

- b) DP Alt Mode: Pass if time is < 100 ps, otherwise fail. While using 50ps (20% to 80%) rise time

- 5. Repeat steps 2 through 4 for each connection for the given DUT

#### Rohde & Schwarz

The Rohde & Schwarz electronics group offers innovative solutions in the following business fields: test and measurement, broadcast and media, secure communications, cybersecurity, monitoring and network testing. Founded more than 80 years ago, the independent company which is headquartered in Munich, Germany, has an extensive sales and service network with locations in more than 70 countries.

www.rohde-schwarz.com

Certified Quality Management ISO 9001

## **Rohde & Schwarz training**

www.rohde-schwarz.com/training

# Rohde & Schwarz customer support

www.rohde-schwarz.com/support

R&S@ is a registered trademark of Rohde & Schwarz GmbH & Co. KG Trade names are trademarks of the owners.

1SLXXX | Version 1a | 07.2024

Application Note | Method of Implementation (MOI) for DisplayPort 80 Compliance Tests

Data without tolerance limits is not binding | Subject to change © 2025 Rohde & Schwarz GmbH & Co. KG | 81671 Munich, Germany www.rohde-schwarz.com