# Interface Control Document R&S®SMW-K506

ARB descriptor word (ADW) and control descriptor word (CDW)

## Products:

► R&S<sup>®</sup>SMW200A

R&S® Munich | ICD | Version 1.2 | 02.2025 https://www.rohde-schwarz.com/appnote/1GP134

| Version | Date       | Author     | Comments                                                                   |

|---------|------------|------------|----------------------------------------------------------------------------|

| 1.2     | 01.02.2025 | R&S Munich | <ul> <li>Correction of faulty references</li> </ul>                        |

|         |            |            | <ul> <li>Additional information on network interface properties</li> </ul> |

| 1.1     | 02.04.2024 | R&S Munich | <ul> <li>Additional information on network interface properties</li> </ul> |

| 1.0     | 04.05.2022 | R&S Munich | <ul> <li>First version</li> </ul>                                          |

# Contents

| 1                                | Overview                                                                                                                  | 5      |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------|

| 1.1<br>1.2<br>1.3<br>1.4         | Document Scope<br>Document Overview<br>Further/Reference Documents<br>Abbreviations and Definitions                       | 5<br>5 |

| 2                                | R&S Descriptor Word Structure                                                                                             | 6      |

| 2.1                              | General Descriptor Word Format Specification                                                                              | 6      |

| 2.1.1<br>2.1.2<br>2.1.3<br>2.1.4 | General Descriptor Word Content<br>Times<br>Bit and Byte Ordering Criteria<br>Reserved and Spare Bits                     | 6<br>6 |

| 2.2                              | ARB Descriptor Word (ADW)                                                                                                 | 7      |

| 2.2.1<br>2.2.2<br>2.2.3          | ARB Descriptor Word Data Content<br>ARB Descriptor Word Bits Allocation<br>ARB segment streaming (rates and memory usage) | 9      |

| 2.3                              | Control Descriptor Word (CDW)1                                                                                            | 0      |

| 2.3.1<br>2.3.2                   | Control Descriptor Word Data Content1<br>Control Descriptor Words Bits Allocation                                         |        |

| 3                                | Timing requirements1                                                                                                      | 2      |

| 3.1                              | ADW Processing1                                                                                                           | 2      |

| 3.1.1<br>3.1.2                   | Deterministic Mode Processing1<br>Instant Mode Processing1                                                                |        |

| 4                                | Network Interface Properties1                                                                                             | 4      |

| 5                                | Appendix1                                                                                                                 | 5      |

| A                                | Examples1                                                                                                                 | 5      |

| A.1<br>A.2<br>A.3                | ADW with Extension                                                                                                        | 6      |

# **List of Tables**

| TABLE 1: ABBREVIATIONS                                                          | 6  |

|---------------------------------------------------------------------------------|----|

| TABLE 2: GENERAL DESCRIPTOR WORD DATA CONTENT                                   | 6  |

| TABLE 3: ADW HEADER STRUCTURE                                                   | 7  |

| TABLE 4: ADW FLAGS STRUCTURE                                                    | 8  |

| TABLE 5: ADW BODY STRUCTURE                                                     | 8  |

| TABLE 6: ADW PAYLOAD STRUCTURE                                                  | 8  |

| TABLE 7: ADW EXTENSION STRUCTURE IF USE_EXTENSION=1                             | 9  |

| TABLE 8: ADW EXTENSION STRUCTURE IF USE_EXTENSION=0                             | 9  |

| TABLE 9: BITS ALLOCATION OF ADW WITHOUT EXTENSION                               | 9  |

| TABLE 10: OVERVIEW ABOUT RELATION OF MAX. ARB SAMPLE RATE, WAVEFORM CLOCK RATE, |    |

| MIN. SEGMENT LENGTH AND MEMORY USAGE                                            | 10 |

| TABLE 11: CDW HEADER STRUCTURE                                                  |    |

| TABLE 12: CDW FLAG STRUCTURE                                                    | 11 |

| TABLE 13: CDW BODY STRUCTURE                                                    |    |

| TABLE 14: BITS ALLOCATION OF CDW                                                | 12 |

| TABLE 15: NETWORK INTERFACE PROPERTIES                                          |    |

| TABLE 16: ADW EXAMPLE TO REPLAY A SEGMENT WITH BURST EXTENSION                  |    |

| TABLE 17: ADW EXAMPLE TO REPLAY A SEGMENT WITHOUT EXTENSION                     | 16 |

| TABLE 18: CDW EXAMPLE TO SWITCH INSTRUMENT RF LEVEL AND FREQUENCY               | 17 |

# 1 Overview

# 1.1 Document Scope

The present R&S®SMW-K506 Interface Control Document contains information on

- the R&S descriptor word format, including ARB descriptor words and control descriptor words in deterministic and instant mode

- ► Timing requirements and limitations of the interface

- ▶ Properties of the network interface (Connector designation: HS DIGIQ).

It is intended for use by customers using descriptor words to control the R&S®SMW200A in real-time. The interface control document specifies the interface between the customer's hardware used for provision of descriptor words and the R&S®SMW200A HS DIGIQ interface. Additional information on descriptor word processing inside the R&S®SMW200A is provided.

Agile Sequencing (R&S®SMW-K506) is supported for SMW FW version 5.00.166.20 and higher.

## 1.2 Document Overview

The present document is organized as follows:

- Chapter 1 is this introduction which provides the scope of the document and further reference and introduces a list of abbreviations and definitions

- Chapter 2 provides the R&S descriptor word structure, including ARB descriptor words and control descriptor words in deterministic and instant mode

- Chapter 3 provides timing requirements for ADW and CDW streaming

- Chapter 4 provides information on the network interface

### 1.3 Further/Reference Documents

- [1] "R&S®SMW-K501/-K502/-K503/-K504/-K315 Extended and Real Time Sequencing, Pulse-on-Pulse Simulation User Manual," Rohde & Schwarz.

- [2] "R&S®SMW200A Vector Signal Generator User Manual," Rohde & Schwarz.

- [3] "Generation of Radar Signals in a Hardware in the Loop (HIL) Environment," Rohde & Schwarz, Application Note.

### **1.4 Abbreviations and Definitions**

The abbreviation "SMW" is used in this document for the Rohde & Schwarz product R&S®SMW200A.

The SMW is a general-purpose vector signal generator with outstanding RF performance. It is capable of generating signals for all main communication, radio and avionic standards and simulating GNSS or radar signals.

Further abbreviations:

| ADW | ARB Descriptor Word     |

|-----|-------------------------|

| CDW | Control Descriptor Word |

Table 1: Abbreviations

# 2 **R&S Descriptor Word Structure**

# 2.1 General Descriptor Word Format Specification

#### 2.1.1 General Descriptor Word Content

The SMW provides a dedicated interface to receive and process R&S Descriptor Words. R&S ARB Descriptor Words (ADW) can be used to replay pre-calculated and pre-stored waveform segments. R&S Control Descriptor Words (CDW) can be used to change RF frequency or level.

| Descriptor Word Type | Purpose                                       |  |

|----------------------|-----------------------------------------------|--|

| ADW                  | Replay pre-calculated waveform (ARB) segments |  |

| CDW                  | Control RF parameters                         |  |

#### Table 2: General Descriptor Word Data Content

Descriptor words are transmitted as sequence of bytes. For all descriptor words, their type is determined by flags in the header. The descriptor word size and content depend on the type.

#### 2.1.2 Times

All times are given as number of clock cycles of the internal 2.4 GHz clock signal.

#### 2.1.3 Bit and Byte Ordering Criteria

All data values are encoded using the following bit and byte ordering criteria:

- ► For numbering, the most significant bit/byte is numbered as bit/byte 0

- ► For bit/byte ordering, the most significant bit/byte is transmitted first (big-endian)

#### 2.1.4 Reserved and Spare Bits

Reserved and spare bits may be used for evolution and can be defined in future updates of this ICD. In order to assure compatibility with future updates, these bits must be set to 0. The same applies for stuffing bits.

# 2.2 ARB Descriptor Word (ADW)

Each ARB descriptor word consists of header, flags, body and payload. The SMW provides two operating modes for ADW streaming: deterministic and instant mode.

The structure for ADWs is the same for both modes. It is highlighted if ADW parameters are only evaluated in one of two operating modes. The difference between deterministic and instant mode is described in Section 3.1.

In this section all ADW components are introduced. The ARB descriptor word format is defined.

#### 2.2.1 ARB Descriptor Word Data Content

The header and flags section of each ADW contain information about the content (structure) of the ADW. Information about the RF characteristics of the desired signal are given in the body section. The payload section addresses a pre-calculated ARB segment. The extension section can be used to play back multiple, identical segments by means of a single ADW (bursts).

#### 2.2.1.1 Header

| ADW header             |         |                                                                        | 56 Bit |

|------------------------|---------|------------------------------------------------------------------------|--------|

| Parameter Data type De |         | Description                                                            | Size   |

| RSVD                   | -       | Reserved for future use                                                | 52 Bit |

| SEG                    | Boolean | 0 = not supported<br>1 = ARB segment                                   | 1 Bit  |

| USE_EXTENSION          | Boolean | 0 = ADW extension block is not used<br>1 = ADW extension block is used | 1 Bit  |

| RSVD                   | -       | Reserved for future use                                                | 2 Bit  |

The ADW header section contains flags which define the content of the ADW.

Table 3: ADW Header Structure

#### 2.2.1.2 Flags

The ADW flags section contains information about the xDW type, interrupt mode and marker settings.

| ADW flags             |           |                                                                                                                                                                                                                                                                                                                 | 8 Bit |

|-----------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Parameter             | Data type | Description                                                                                                                                                                                                                                                                                                     | Size  |

| CTRL                  | Boolean   | Indicates whether the descriptor word is an ADW or a<br>CDW<br>0 = ADW<br>1 = CDW                                                                                                                                                                                                                               | 1 Bit |

| SEG_INTERRUPT Boolean |           | Indicates whether the addressed segment can be<br>interrupted by a subsequent segment or is played until<br>the last sample.<br>0 = Played until last sample of segment<br>1 = Can be interrupted by subsequent ADW<br>If the burst extension is used, the flag is valid for all<br>repetitions of the segment. | 1 Bit |

| RSVD                  | -         | Reserved for future use                                                                                                                                                                                                                                                                                         | 1 Bit |

| IGNORE_ADW Boolean |         | ADW is ignored (no signal output) | 1 Bit |

|--------------------|---------|-----------------------------------|-------|

| M4 Boolean         |         | Reserved                          | 1 Bit |

| M3                 | Boolean | Set Marker 3                      | 1 Bit |

| M2                 | Boolean | Set Marker 2                      | 1 Bit |

| M1                 | Boolean | Set Marker 1                      | 1 Bit |

Table 4: ADW Flags Structure

#### 2.2.1.3 Body

The ADW body section contains offset values for frequency, level and phase relative to the instrument RF settings.

| ADW body     |              |                                                                                                                                                         | 64 Bits |

|--------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Parameter    | Data type    | Description                                                                                                                                             | Size    |

| FREQ_OFFSET  | int          | Frequency offset added to instrument RF frequency.<br>-1 GHz <= frequency_offset <= 1 GHz<br>FREQ_OFFSET = (frequency_offset / 2.4e9) * 2 <sup>32</sup> | 32 Bit  |

| LEVEL_OFFSET | unsigned int | Level offset subtracted from instrument RF level.<br>level_offset >= 0 dB<br>LEVEL_OFFSET = 10 <sup>(-level_offset / 20)</sup> * 2 <sup>15</sup>        | 16 Bit  |

| PHASE_OFFSET | unsigned int | Phase offset<br>0° <= phase_offset < 360°<br>PHASE_OFFSET = phase_offset/360° * 2 <sup>16</sup>                                                         | 16 Bit  |

Table 5: ADW Body Structure

#### 2.2.1.4 Payload

The payload section contains the segment index of a pre-calculated waveform.

| ADW payload |              |                                                                                       | 80 Bit |

|-------------|--------------|---------------------------------------------------------------------------------------|--------|

| Parameter   | Data type    | Description                                                                           | Size   |

| SEGMENT     | unsigned int | Index of the pre-calculated waveform, which was loaded into the SMW memory in advance | 24 Bit |

| RSVD        | -            | Reserved for future use                                                               | 56 Bit |

Table 6: ADW Payload Structure

#### 2.2.1.5 Extension

The 6 Byte extension is evaluated if the USE\_EXTENSION bit in the header is set to 1. If USE\_EXTENSION=0, all extension fields should be filled with zeros.

| Extension fields [USE_EXTENSION=1] |   |                                                                                                                |        |

|------------------------------------|---|----------------------------------------------------------------------------------------------------------------|--------|

| Parameter Data type Description    |   |                                                                                                                | Size   |

| BURST_SRI                          | Ū | Segment repetition interval (SRI) from first sample to<br>first sample<br>BURST_SRI = (SRI in seconds) * 2.4e9 | 32 Bit |

| BURST_ADD_SEGMENTS | unsigned int | Number of repetitions in addition to the initial segment | 16 Bit |

|--------------------|--------------|----------------------------------------------------------|--------|

|                    |              | 0 = infinite repetitions                                 |        |

|                    |              | (do not use with SEG_INTERRUPT = 0)                      |        |

#### Table 7: ADW Extension Structure if USE\_EXTENSION=1

| Extension fields [USE_EXTENSION=0] |   |             |        |  |  |

|------------------------------------|---|-------------|--------|--|--|

| Parameter Data type Description S  |   |             |        |  |  |

| STUFFING                           | - | Fill with 0 | 48 Bit |  |  |

Table 8: ADW Extension structure if USE\_EXTENSION=0

#### 2.2.2 ARB Descriptor Word Bits Allocation

An ADW consists of header, flags, body, payload and extension. The extension content depends on the USE\_EXTENSION flag in the header. Table 9 shows the bit allocation for an ADW.

| Header | Flags | Body | Payload | Extension | Total<br>(bits) |

|--------|-------|------|---------|-----------|-----------------|

| 56     | 8     | 64   | 80      | 48        | 256             |

Table 9: Bits allocation of ADW without extension

#### 2.2.3 ARB segment streaming (rates and memory usage)

ARB segments have to be uploaded to the SMW before starting the simulation. This can be performed via the SMW GUI or remotely with SCPI commands.

A table showing all preloaded segments can be accessed via the SMW GUI.

| Segment Index | Filename              | Clock Rate  | Samples | Length     | Path       | Info |

|---------------|-----------------------|-------------|---------|------------|------------|------|

| 0             | Pulse_10us_1000MHz.wv | 1.000 GHz   | 100000  | 100.000 µs | /var/user/ | Info |

| 1             | Pulse_20us_1000MHz.wv | 1.000 GHz   | 100000  | 100.000 µs | /var/user/ | Info |

| 2             | Pulse_30us_1000MHz.wv | 1.000 GHz   | 100000  | 100.000 µs | /var/user/ | Info |

| 3             | Pulse_30us_500MHz.wv  | 500.000 MHz | 50000   | 100.000 µs | /var/user/ | Info |

| 4             | Pulse_30us_50MHz.wv   | 50.000 MHz  | 5000    | 100.000 µs | /var/user/ | Info |

Figure 1: Pre-calculated segment table view in the SMW200A GUI

Each individual waveform is assigned a segment index (first column) which is used inside the ADW (SEGMENT in ADW payload) to address the respective waveform segment.

All waveforms appended to this list are internally resampled to a common clock rate. A container file is automatically created, which is downloaded to the memory of the coder board. After this, the SMW is ready to receive ADWs with a segment index to select and play a waveform.

In order to reach high ADW streaming rates with ARB segments, the SMW firmware up-samples the user waveforms before processing them in hardware to minimize the hardware resampling delay. This in turn leads to a higher memory usage.

The desired ARB sample rate can be selected in the SMW200A GUI:

| Extended Sequencer A: Waveform List - /var/user/as_test_list.inf_mswv                                                  |                |            |         |        |     |            |  |      |  |

|------------------------------------------------------------------------------------------------------------------------|----------------|------------|---------|--------|-----|------------|--|------|--|

| Desired ARB Sample Rate 2.4 GHz Affects ARB Memory Usage (the higher the sample rate, the higher the ARB memory usage) |                |            |         |        |     |            |  |      |  |

| Segment Index                                                                                                          | Filename       | Clock Rate | Samples | Length |     | Path       |  | Info |  |

| 0                                                                                                                      | CWI_0_25Q_0.wv | 10.000 MHz | 100     | 10.000 | μs  | /var/user/ |  | Info |  |

|                                                                                                                        |                |            | Desir   | ed ARB | Sar | mple Rate  |  |      |  |

| 1                                                                                                                      | CWI_0Q_0.wv    |            |         |        |     | 37.5 MHz   |  | Info |  |

| 2                                                                                                                      | CWI_0Q_0_25.w  |            |         |        |     | 75 MHz     |  | Info |  |

| 3                                                                                                                      | CW_I_0Q_m0_25. |            |         |        |     |            |  | Info |  |

| -                                                                                                                      |                |            |         |        |     | 300 MHz    |  |      |  |

|                                                                                                                        |                |            |         |        |     | 🔒 2.4 GHz  |  |      |  |

Figure 2: Selection of desired ARB Sample Rate in SMW200A GUI

The selected sample rate determines the waveform clock rate after resampling and consequently the memory usage. The following table provides an overview about desired ARB segment sample rate, waveform clock rate, minimum segment length and as an example minimum memory usage for 1000 segments with a lengths of 100  $\mu$ s each.

| Desired ARB Sample<br>Rate | Waveform Clock Rate                                  | length <sup>1</sup> | Minimum Memory Usage<br>(1000 segments; 100 μs<br>per segment)² |

|----------------------------|------------------------------------------------------|---------------------|-----------------------------------------------------------------|

| 37.5 MHz                   | max(37.5 MHz, highest clock rate of loaded segments) | 27.3 µs             | 15 MByte                                                        |

| 75 MHz                     | max(75 MHz, highest clock rate of loaded segments)   | 13.7 µs             | 30 MByte                                                        |

| 300 MHz                    | max(300 MHz, highest clock rate of loaded segments)  | 3.41 µs             | 120 MByte                                                       |

| 2.4 GHz                    | 2.4 GHz                                              | 427 ns              | 960 Mbyte                                                       |

Table 10: Overview about relation of max. ARB sample rate, waveform clock rate, min. segment length and memory usage

The 24 Bit SEGMENT field inside the R&S ADW theoretically allows to address  $2^{24} = 16.777.216$  individual waveforms. The maximum number of segments with minimum segment size is 2 million.<sup>2</sup>

## 2.3 Control Descriptor Word (CDW)

By setting the CTRL flag in the xDW flags section, the user can issue commands such as changing the instrument RF frequency and/or amplitude of the signal generator directly from the descriptor word, where otherwise a SCPI command would have been necessary.

As with ADWs, the content and layout of CDWs is the same for both deterministic and instant mode.

<sup>&</sup>lt;sup>1</sup> Minimum RAM granularity = 1024 Samples

<sup>&</sup>lt;sup>2</sup> Max. Memory size = 2 GSamples (requires SMW-K515)

### 2.3.1 Control Descriptor Word Data Content

A CDW consists of header, flags and body. The header and flags of each CDW specify the command type. Information about the instrument RF settings are given in the body section.

#### 2.3.1.1 Header

The CDW header section contains flags which define the command type.

| CDW header | 56 Bit       |                                                                                                              |        |

|------------|--------------|--------------------------------------------------------------------------------------------------------------|--------|

| Parameter  | Data type    | Description                                                                                                  | Size   |

| RSVD       | -            | Reserved for future use                                                                                      | 52 Bit |

| PATH       | Boolean      | Specifies RF path which is affected by CDW<br>0 = Path A<br>1 = Path B                                       | 1 Bit  |

| CMD        | unsigned int | Specifies command type<br>0 = Frequency change<br>1 = Amplitude change<br>2 = Frequency and amplitude change | 3 Bit  |

Table 11: CDW Header Structure

#### 2.3.1.2 Flags

The CDW flags section contains information about the xDW type.

| CDW flags |           |                                                                               |       |  |  |  |

|-----------|-----------|-------------------------------------------------------------------------------|-------|--|--|--|

| Parameter | Data type | Description                                                                   | Size  |  |  |  |

| CTRL      | Boolean   | Indicates whether descriptor word is an ADW or a<br>CDW<br>0 = ADW<br>1 = CDW | 1 Bit |  |  |  |

| RSVD      | -         | Reserved for future use                                                       | 7 Bit |  |  |  |

Table 12: CDW Flag Structure

#### 2.3.1.3 Body

The CDW body section contains values for instrument RF frequency and level.

| CDW body  |                       |         |                                                |                 |               |                   |                      | 64 Bit |  |

|-----------|-----------------------|---------|------------------------------------------------|-----------------|---------------|-------------------|----------------------|--------|--|

| Parameter | Data type             | Descr   | Description                                    |                 |               |                   |                      |        |  |

| FVAL      | unsigned int          | RF free | RF frequency setting of signal generator in Hz |                 |               |                   |                      |        |  |

| LVAL      | signed<br>fixed point |         | RF level setting of signal generator in dBm    |                 |               |                   |                      |        |  |

|           | BCD                   | Bit     | 0                                              | 1-7             | 8-11          | 12-15             | 16-23                |        |  |

|           |                       | Value   | Sign<br>0=pos<br>1=neg                         | Integer<br>part | Tenth<br>part | Hundredth<br>part | Unused<br>(Set to 0) |        |  |

Table 13: CDW Body Structure

#### 2.3.2 Control Descriptor Words Bits Allocation

| Header | Flags | Body | Total<br>(bits) |

|--------|-------|------|-----------------|

| 56     | 8     | 64   | 128             |

The bit allocation of a CDW is shown in the following table.

Table 14: Bits allocation of CDW

# **3 Timing requirements**

## 3.1 ADW Processing

The SMW provides two modes for ADW streaming. The deterministic mode should be used if there are strict timing requirements for segment playback. If this is not required, instant mode can be used where segments are played back as soon as the ADW has been processed. The operating mode can be configured in the SMW GUI or via SCPI command (see R&S®SMW200A Manual).

Irrespective of the operating mode, the SMW features a receive buffer (FIFO) for 512 ADWs. ADWs are taken out of this FIFO at a maximum rate of 1 ADW/µs or 1 MADW/s (see Minimum ARB segment playback repetition interval in R&S®SMW200A datasheet). This has to be considered at the transmit side. The flow control is within the responsibility of the user.

For the following sections the convention is as follows:

- ADW #x addresses segment #x (referred to as current ADW and current segment)

- ADW #y addresses segment #y (referred to as next ADW and next segment)

#### 3.1.1 Deterministic Mode Processing

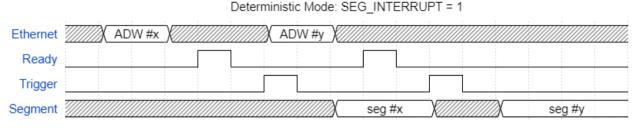

In deterministic mode, once an ADW arrives at the HS DIGIQ interface, the data is unpacked and written into a buffer. When the ADW is taken from the FIFO, the addressed ARB segment is loaded and a ready-marker is provided at the configured global or local connector. The user can then trigger the playback of the next segment (see R&S®SMW200A Manual for Trigger/Marker configuration). After the segment was triggered, the next ADW in line is processed. This process is illustrated in Figure 4 and Figure 4.

#### **SEG\_INTERRUPT = 0**

In case the SEG\_INTERRUPT flag of the current ADW (ADW #x) was set to 0, the ready marker for the next ADW (ADW #y) is delayed until the current segment (segment #x) has been played until the last sample. Deterministic Mode: SEG\_INTERRUPT = 0

| Ethernet | ADW #x | X///////////////////////////////////// |   | ADW #y | X/////// |        |        |  |        |

|----------|--------|----------------------------------------|---|--------|----------|--------|--------|--|--------|

| Ready    | <br>   |                                        | 1 |        |          |        |        |  |        |

| Trigger  | <br>   |                                        |   |        |          |        |        |  |        |

| Segment  |        |                                        |   |        | X        | seg #x | X///// |  | seg #y |

Figure 3: Timing diagram of segment playback in deterministic mode with SEG\_INTERRUPT=0 in ADW #x

### SEG\_INTERRUPT = 1

In case the SEG\_INTERRUPT flag of the current ADW (ADW #x) was set to 1, the ready marker for the next ADW (ADW #y) is provided as soon as the ADW was processed. Triggering the next segment (segment #y) immediately interrupts the current segment (segment #x).

Figure 4: Timing diagram of segment playback in deterministic mode with SEG\_INTERRUPT = 1 in ADW #x

The delay between the rising trigger edge and the segment appearing at the RF output is deterministic up to the jitter given in the R&S®SMW200A datasheet. This delay depends on the configured ARB sample rate and is also given in the R&S®SMW200A datasheet. The ARB sample rate can be configured on creation of an ARB segment list.

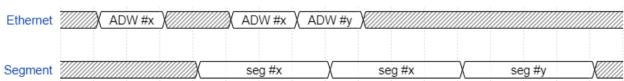

#### 3.1.2 Instant Mode Processing

In instant mode, ARB segments are played back as soon as possible, without the need for an external trigger. In this mode, the delay between the arrival of the ADW at the HS DIGIQ interface at the SMW and the signal appearing at the RF output of the SMW is not deterministic.

#### SEG\_INTERRUPT = 0

If the SEG\_INTERRUPT flag is set to 0, the segment is always played back until the last sample. Playback is not interrupted by other successively arriving ADWs (See Figure 5).

```

Instant Mode: SEG_INTERRUPT = 0

```

Figure 5: Timing diagram for segment playback in instant mode with SEG\_INTERRUPT=0 in ADW #x

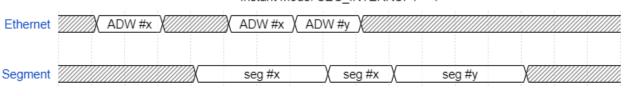

#### SEG\_INTERRUPT = 1

If the SEG\_INTERRUPT flag is set to 1, the playback of the currently played segment is interrupted to start the playback of the segment addressed by a successively arriving ADW as soon as possible (see Figure 6).

Instant Mode: SEG\_INTERRUPT = 1

Figure 6: Timing diagram for segment playback in instant mode with SEG\_INTERRUPT=1 in ADW #x

# **4 Network Interface Properties**

| Connector designation       | HS DIGIQ                                       |

|-----------------------------|------------------------------------------------|

| Mechanical connector        | QSFP+ / QSFP 28                                |

| Mandatory adapter           | 40G QSFP+ to 10G SFP+ adapter converter module |

| Supported data rates        | 10 Gbit/s                                      |

| Supported network protocols | UDP over Ethernet                              |

Table 15: Network interface properties

The figure below illustrates the connection between the SMW200A HS DIGIQ interface and a PC with a 10G SFP+ ethernet network interface.

Figure 7: Connection between the SMW200A HS DIGIQ interface and a PC with a 10G SFP+ ethernet network interface

Note: ADW/CDW streaming is only supported for point-to-point connections between a user equipment's network interface and the SMW200A HS DIGIQ interface. Routing via hubs, switches or routers is not supported!

#### Ethernet

The Maximum Transmission Unit (MTU) size of the Ethernet controller must be set to 1500 (Bytes). This is the default value for most network interface controllers.

#### UDP

Sending ADWs via UDP to the SMW, it must be considered that the sender application is responsible for fragmenting the ADW data into UDP datagrams of an appropriate size.

To improve real-time capability, the Address Resolution Protocol (ARP) table of the sender should be up-todate before starting to send UDP datagrams. Otherwise, the first datagram will be possibly sent delayed, since the sender has to send an ARP request and wait for the response to update his ARP table before. This can be done by sending empty UDP datagrams to the SMW interface. The procedure has to be repeated depending on the ARP table timeout of the sender.

# **5** Appendix

# **A** Examples

#### A.1 ADW with Extension

| Parameter Parameter Value |           | Meaning      | Binary Data                             |

|---------------------------|-----------|--------------|-----------------------------------------|

| ADW Header                |           |              | ·                                       |

| RSVD                      | 0         | -            |                                         |

| RSVD                      | 0         | -            | 0x0000000000004                         |

| USE_EXTENSION             | 1         | True         | 0x0000000000004                         |

| RSVD                      | 0         | -            |                                         |

| ADW Flags                 |           |              |                                         |

| CTRL                      | 0         | False        |                                         |

| SEG_INTERRUPT             | 0         | False        |                                         |

| RSVD                      | 0         | -            |                                         |

| IGNORE_ADW                | 0         | False        | 0x01                                    |

| M4                        | 0         | -            | 0x01                                    |

| М3                        | 0         | Marker 3 off |                                         |

| M2                        | 0         | Marker 2 off |                                         |

| M1                        | 1         | Marker 1 on  |                                         |

| ADW Body                  |           |              |                                         |

| FRQ                       | -14660155 | -125 MHz     |                                         |

| LEV                       | 23198     | 3 dB         | 0xf2aaaaaa5a9e5555                      |

| PHS                       | 21845     | 120°         |                                         |

| ADW Payload               |           |              |                                         |

| SEGMENT                   | 2         | Waveform #2  | 0,0000020000000000000000000000000000000 |

| RSVD                      | 0         | -            | 0x00000200000000000000000               |

| ADW Extension             |           |              |                                         |

| BURST_SRI                 | 192000    | 80 µs        | 0x0002ee000009                          |

| BURST_ADD_SEGMENTS        | 9         | 9            | 0x000266000009                          |

Table 16: ADW example to replay a segment with burst extension

**ADW:** 0x0000000 0x00000401 0xf2aaaaaa 0x5a9e5555 0x00000200 0x00000000 0x00000002 0xee000009

#### A.2 ADW without Extension

| Parameter     | Parameter Value | Meaning       | Binary Data                             |  |  |

|---------------|-----------------|---------------|-----------------------------------------|--|--|

| ADW Header    |                 |               |                                         |  |  |

| RSVD          | 0               | -             |                                         |  |  |

| RSVD          | 0               | -             | 0x0000000000000                         |  |  |

| USE_EXTENSION | 0               | False         | 0x00000000000000                        |  |  |

| RSVD          | 0               | -             |                                         |  |  |

| ADW Flags     |                 |               |                                         |  |  |

| CTRL          | 0               | False         |                                         |  |  |

| SEG_INTERRUPT | 1               | True          |                                         |  |  |

| RSVD          | 0               | -             |                                         |  |  |

| IGNORE_ADW    | 0               | False         |                                         |  |  |

| M4            | 0               | -             | 0X41                                    |  |  |

| М3            | 0               | Marker 3 off  |                                         |  |  |

| M2            | 0               | Marker 2 off  |                                         |  |  |

| M1            | 1               | Marker 1 on   |                                         |  |  |

| ADW Body      |                 |               |                                         |  |  |

| FRQ           | 29320310        | 250 MHz       |                                         |  |  |

| LEV           | 16423           | 6 dB          | 0xcaaaaaaa40261555                      |  |  |

| PHS           | 1820            | 10°           |                                         |  |  |

| ADW Payload   |                 |               |                                         |  |  |

| SEGMENT       | 100             | Waveform #100 | 0,00000 4000000000000000000000000000000 |  |  |

| RSVD          | 0               | -             |                                         |  |  |

| ADW Extension |                 |               |                                         |  |  |

| STUFFING      | 0               | -             | 0,00000000000                           |  |  |

| STUFFING      | 0               | -             | 0x00000000000                           |  |  |

Table 17: ADW example to replay a segment without extension

**ADW**: 0x0000000 0x00000041 0xcaaaaaaa 0x40261555 0x00006400 0x00000000 0x00000000 0x00000000

### A.3 CDW

| Parameter  | Parameter Value | Meaning                        | Binary Data          |  |  |

|------------|-----------------|--------------------------------|----------------------|--|--|

| ADW Header |                 |                                |                      |  |  |

| RSVD       | 0               | -                              | 0x00000000000000000a |  |  |

| РАТН       | 1               | Path B                         |                      |  |  |

| CMD        | 2               | Frequency and amplitude change |                      |  |  |

| ADW Flags  |                 |                                |                      |  |  |

| CTRL       | 1               | True                           | - 0x80               |  |  |

| RSVD       | 0               | -                              |                      |  |  |

| ADW Body   |                 |                                |                      |  |  |

| FVAL       | 1090000000      | 10.9 GHz                       | 0x0289b0cd008d0000   |  |  |

| LVAL       | -7536640        | -13 dBm                        |                      |  |  |

Table 18: CDW example to switch instrument RF level and frequency

**CDW**: 0x0000000 0x00000a80 0x0289b0cd 0x008d0000

### Rohde & Schwarz

The Rohde & Schwarz electronics group offers innovative solutions in the following business fields: test and measurement, broadcast and media, secure communications, cybersecurity, monitoring and network testing. Founded more than 80 years ago, the independent company which is headquartered in Munich, Germany, has an extensive sales and service network with locations in more than 70 countries.

www.rohde-schwarz.com

### Rohde & Schwarz training

www.training.rohde-schwarz.com

#### Rohde & Schwarz customer support

www.rohde-schwarz.com/support

R&S<sup>®</sup> is a registered trademark of Rohde & Schwarz GmbH & Co. KG Trade names are trademarks of the owners. ICD | Version 1.2 | 02.2025 Interface Control Document | R&S®SMW-K506 Data without tolerance limits is not binding | Subject to change © 2025 Rohde & Schwarz GmbH & Co. KG | 81671 Munich, Germany www.rohde-schwarz.com